uchan が 2022年02月18日11時24分49秒 に編集

初版

タイトルの変更

Gowin UART Master IP 2.0の信号タイミングが仕様書と違う

タグの変更

UART

Gowin

Tang-Nano

FPGA

メイン画像の変更

記事種類の変更

セットアップや使用方法

本文の変更

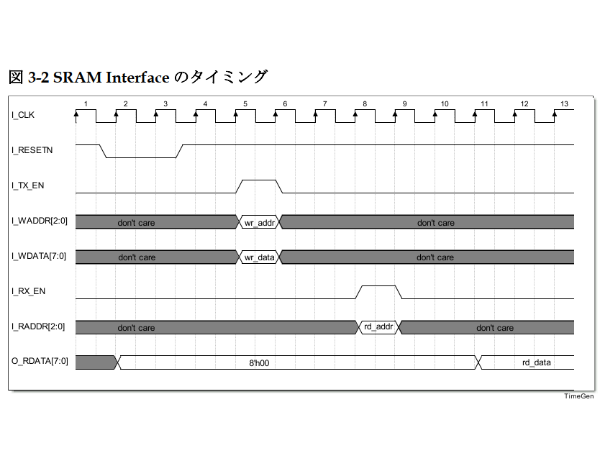

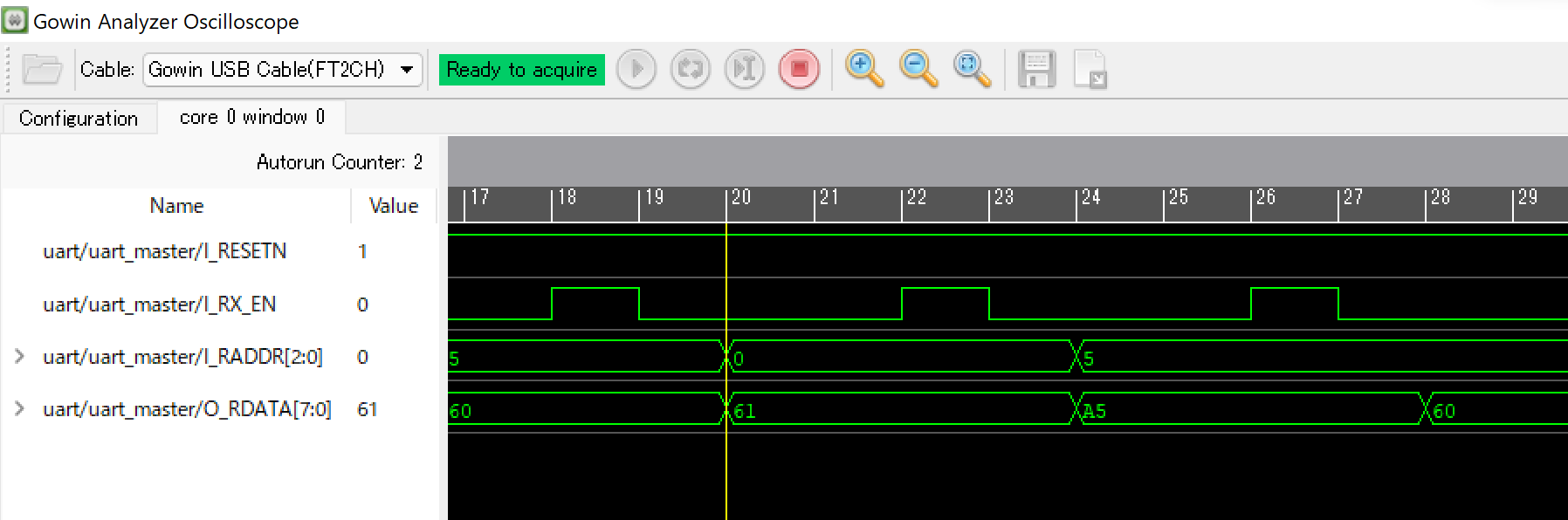

Gowin UART Master IP のユーザーガイド[^uart-ug]バージョン 1.5 に信号のタイミング図が追加されたので、現物のタイミングと比較してみたところ、ユーザーガイドの図と実際のタイミングが異なることが分かりました。 [^uart-ug]: https://www.gowinsemi.com/ja/support/ip_detail/3/ ## ユーザーガイドのタイミング図 下図がバージョン 1.5 で追加された SRAM インターフェースのタイミング図です。  今回注目するのは受信のタイミングです。 I_RX_EN が 1 になった後のクロックの立ち上がりの瞬間(I_CLK の 9 番エッジ)に I_RADDR=rd_addr が UART Master IP コアに取り込まれます。そこから **2 サイクル後**(I_CLK の 11 番エッジ) に O_RDATA の内容が rd_data となります。rd_addr で指定されたレジスタの値が rd_data として取り出せます。 図 3-2 の手前にこのような説明があります。 > インターフェースがある I_CLK クロックの立ち上がりエッジで読み出し要求を検出すると、少なくとももう 2 サイクル待機した後、対応するデータを返します。 文章でも「2 サイクル」と説明されていますね。 ## 実際のタイミング 下図は Tang Nano 4K で UART Master IP 2.0 を動作させたときのタイミング図です。  ユーザーガイドの図と違い、I_RX_EN が 1 になった **1 サイクル後**に O_RDATA が変化していることが分かります。ちなみに、ここで O_RDATA に出力された値は期待通りの値で、特に壊れたりはしていません。 ユーザーガイドの図では、I_RX_EN が 1 になってから 2 サイクルの間は O_RDATA が変化しないように見えますが、現実は違うようです。注意が必要ですね。