rily が 2025年12月23日20時57分51秒 に編集

コメント無し

タグの変更

ダイオード

クランプ回路

本文の変更

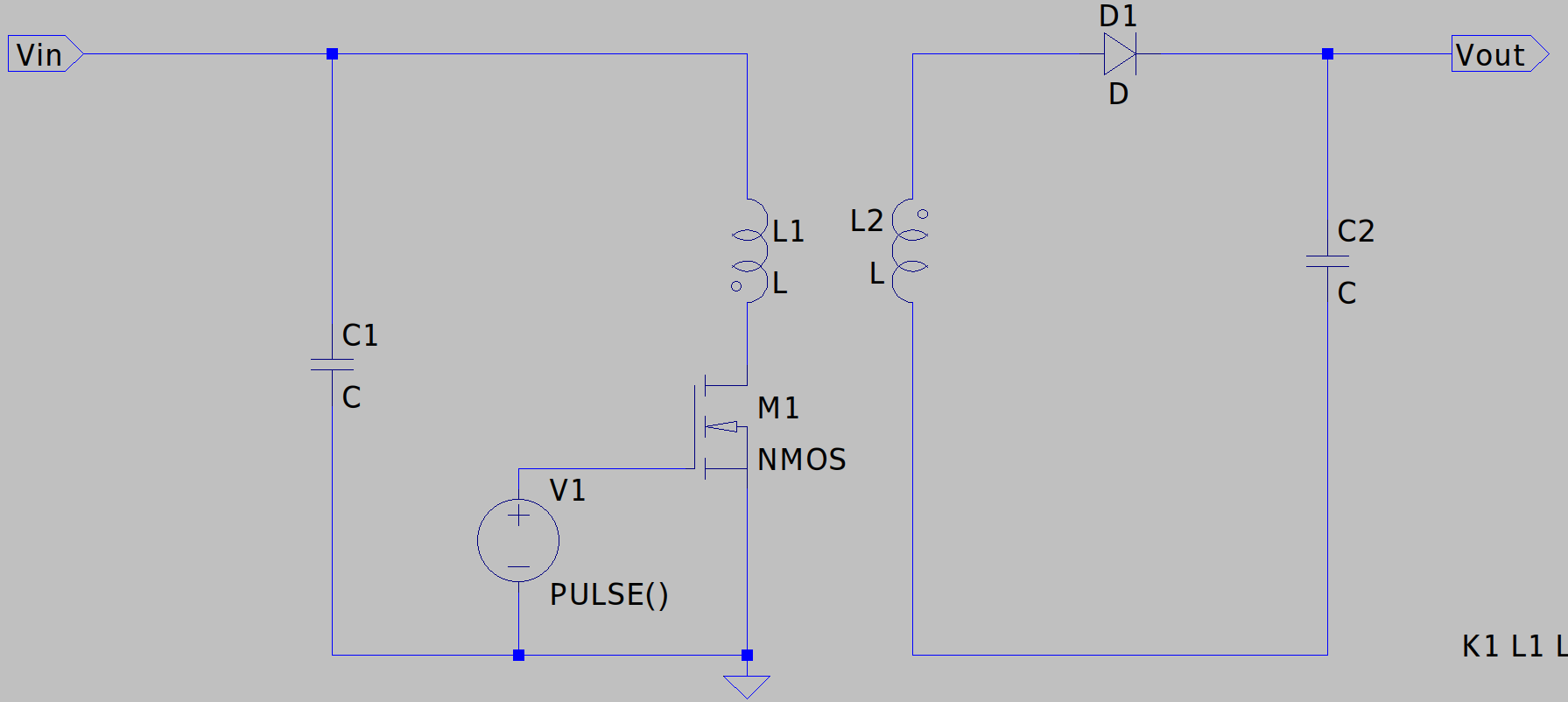

[前回](https://elchika.com/article/11054988-a22e-459f-9a00-41159cc2ce23/)の続きになりますが、今回は一次側サージ電圧をうまく抑えて効率を上げた2スイッチ式コンバータをシミュレーションしてみたいと思います。 2スイッチコンバータ -  こちらが従来の1スイッチフライバックコンバータとなります。この回路、一次側のコイルや漏れインダクタンスから発生する起電力が電源電圧に重畳されるため、非常に高いサージ電圧が発生します。

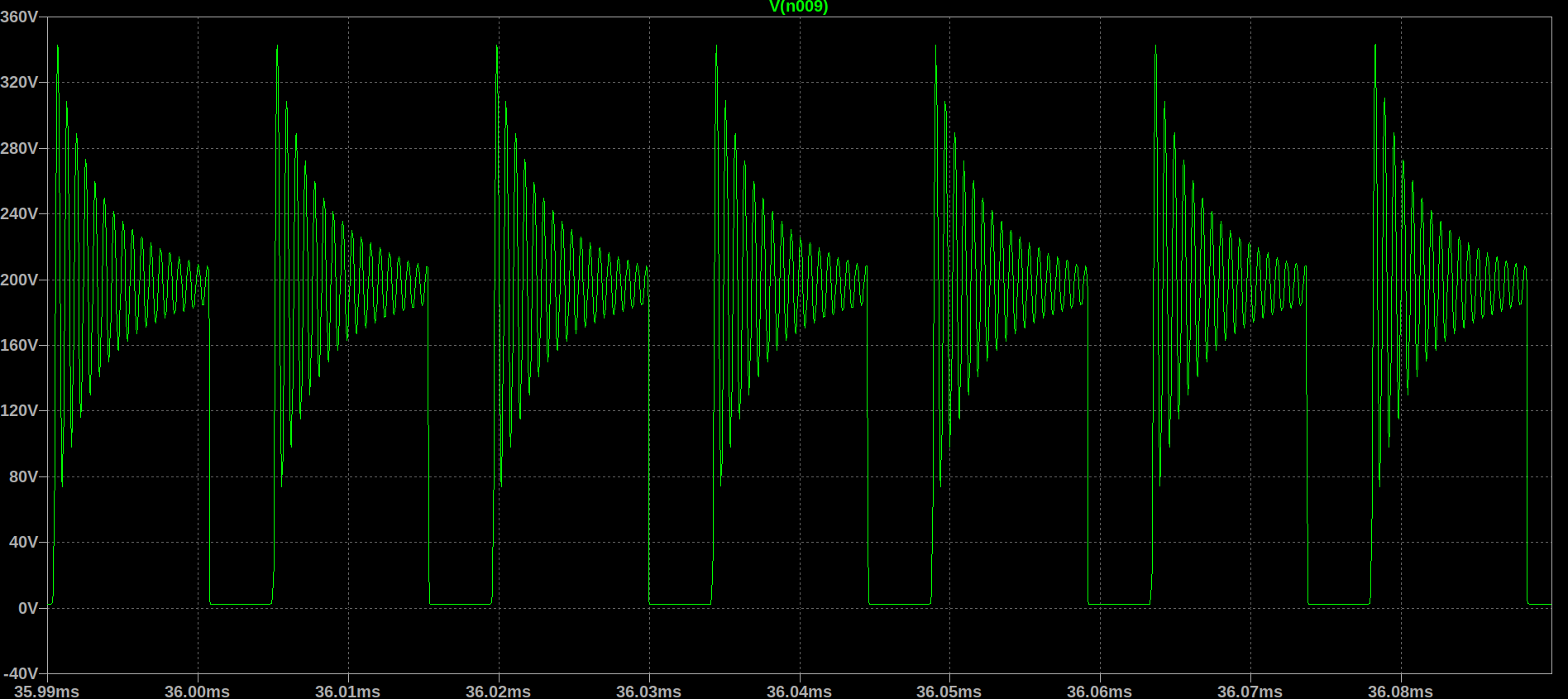

前回の回路の一次サージ波形ですが、対策をしても400V近いサージが発生しているのがわかります。さらに海外の電源電圧は200Vを超える場所もあります。そのため、より耐圧の高いMOSFETを選ぶ必要があり、入手性が悪くなったり、サージ対策やON抵抗増加による効率や発熱の悪化を招く可能性があります。

前回回路の一次サージ波形は、対策をしても400V近いサージが発生しているのがわかります。さらに海外の電源電圧は200Vを超えるため、より耐圧の高いMOSFETを選ぶ必要があり、ON抵抗増加やサージ対策により効率や発熱の悪化を招く可能性があります。またMOSFETは耐圧が高くなるにつれて入手性が悪化する可能性も考えられます。

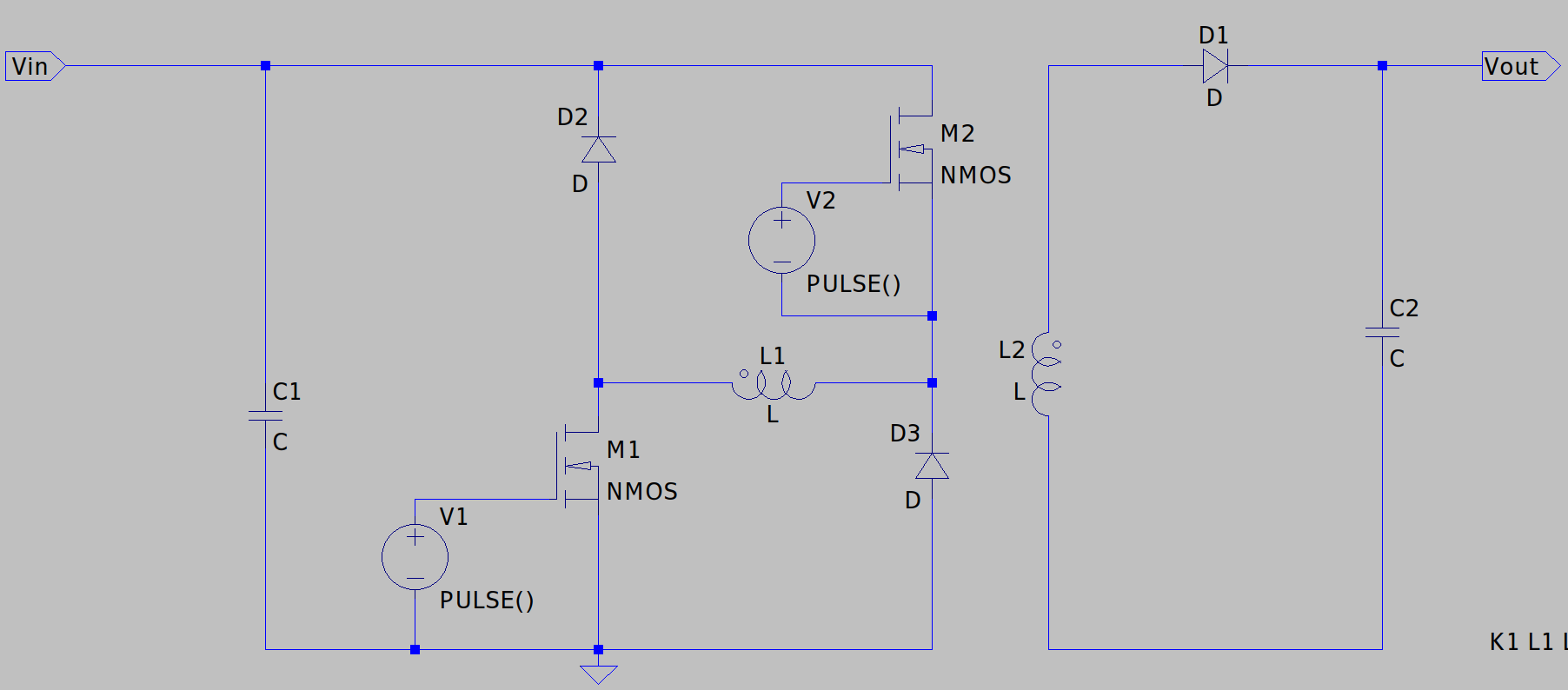

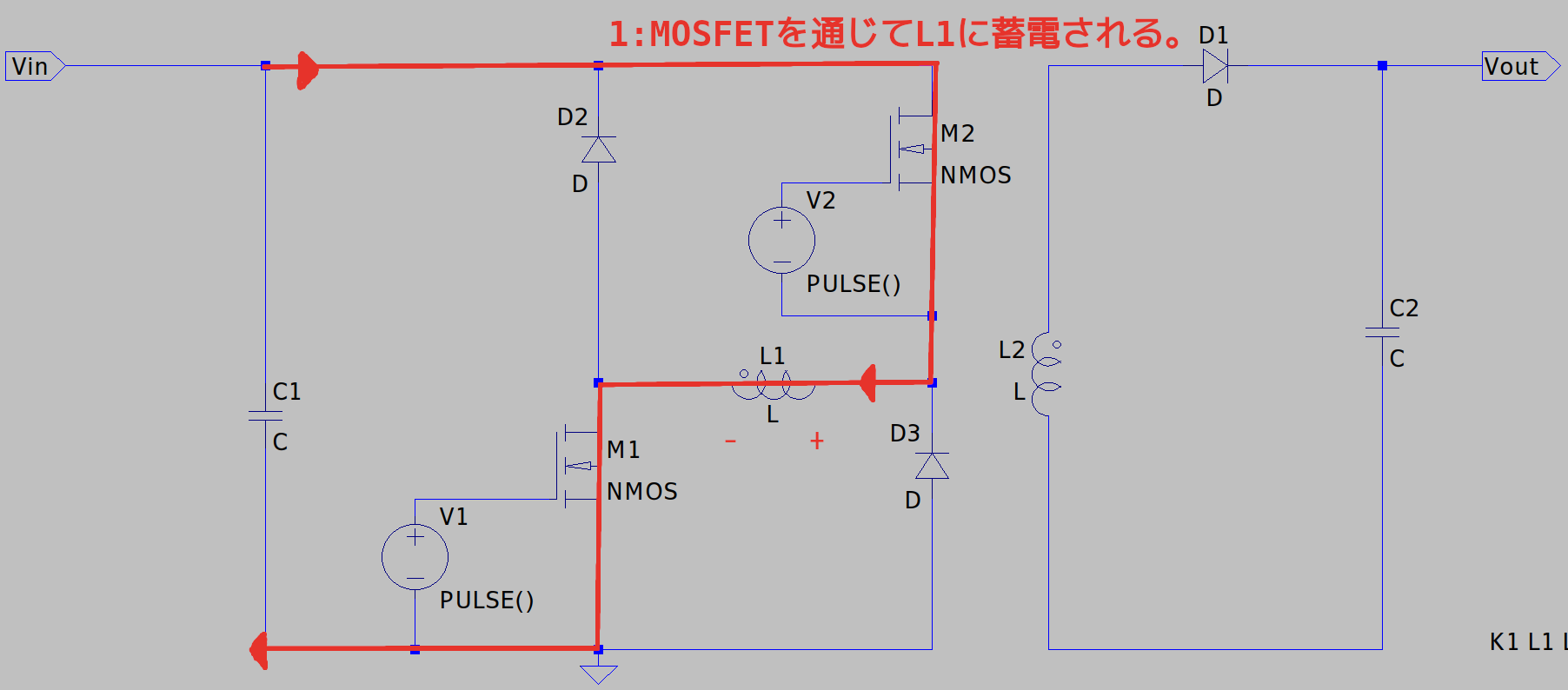

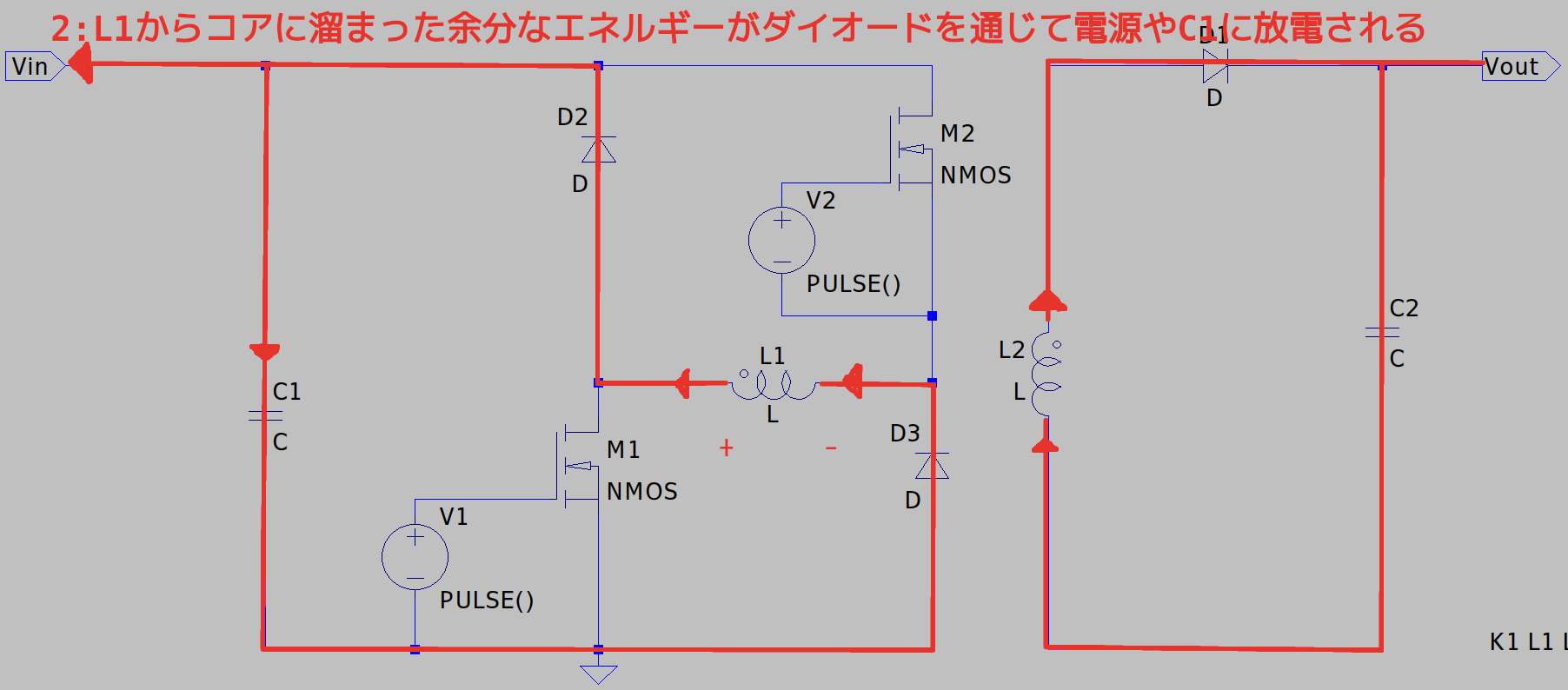

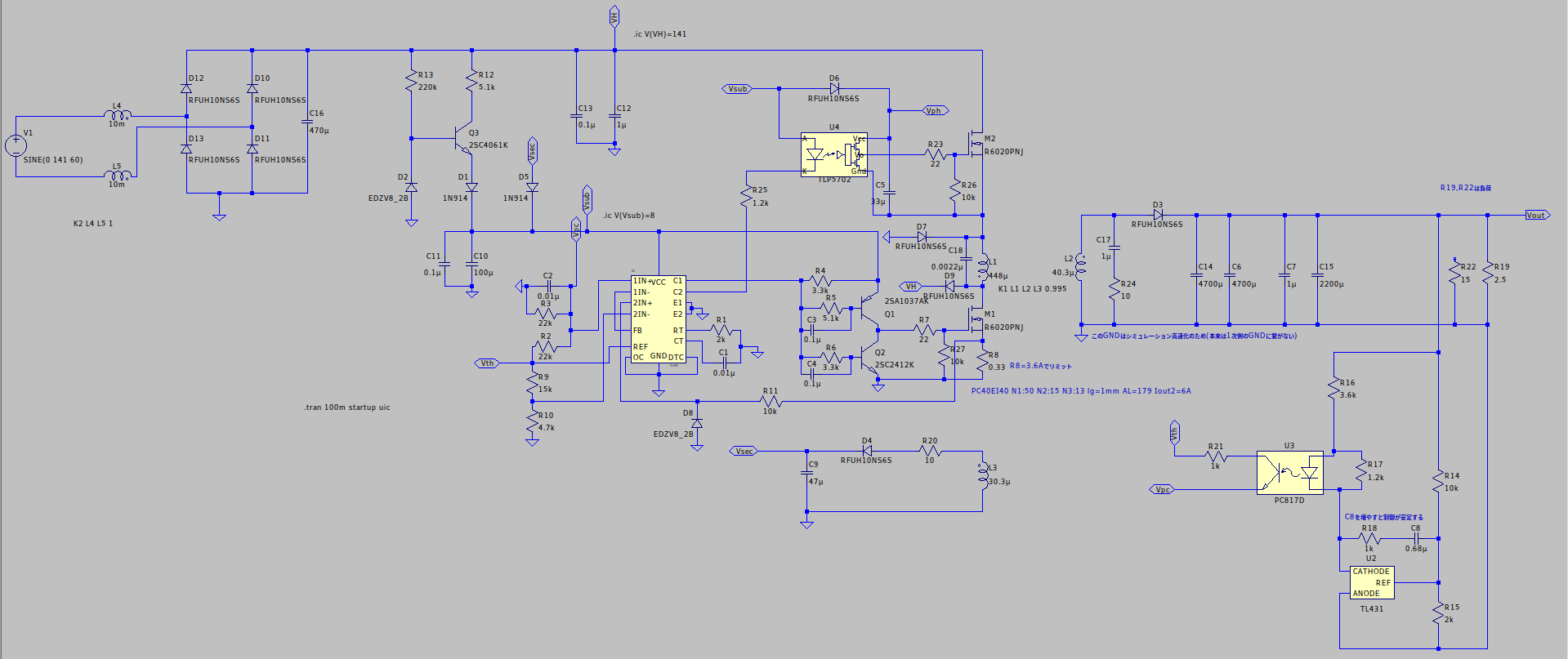

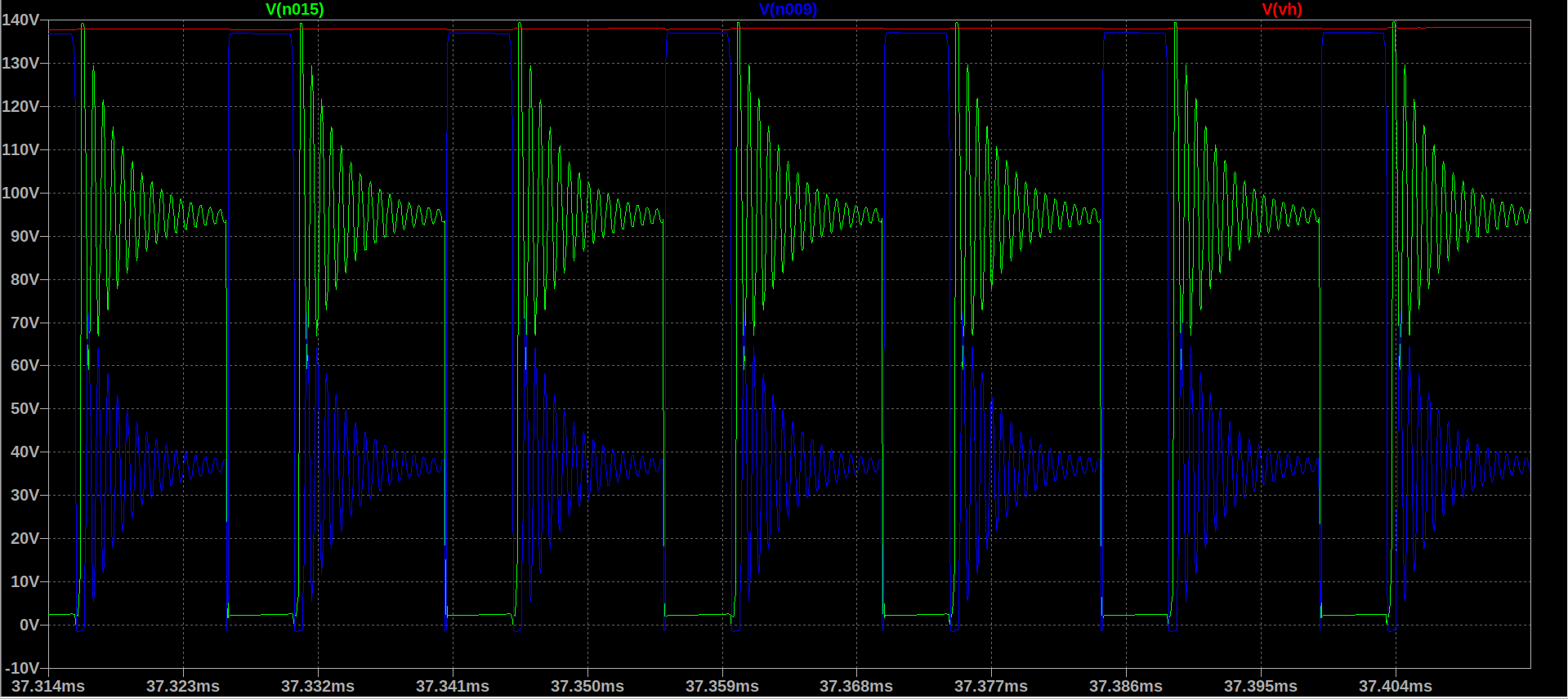

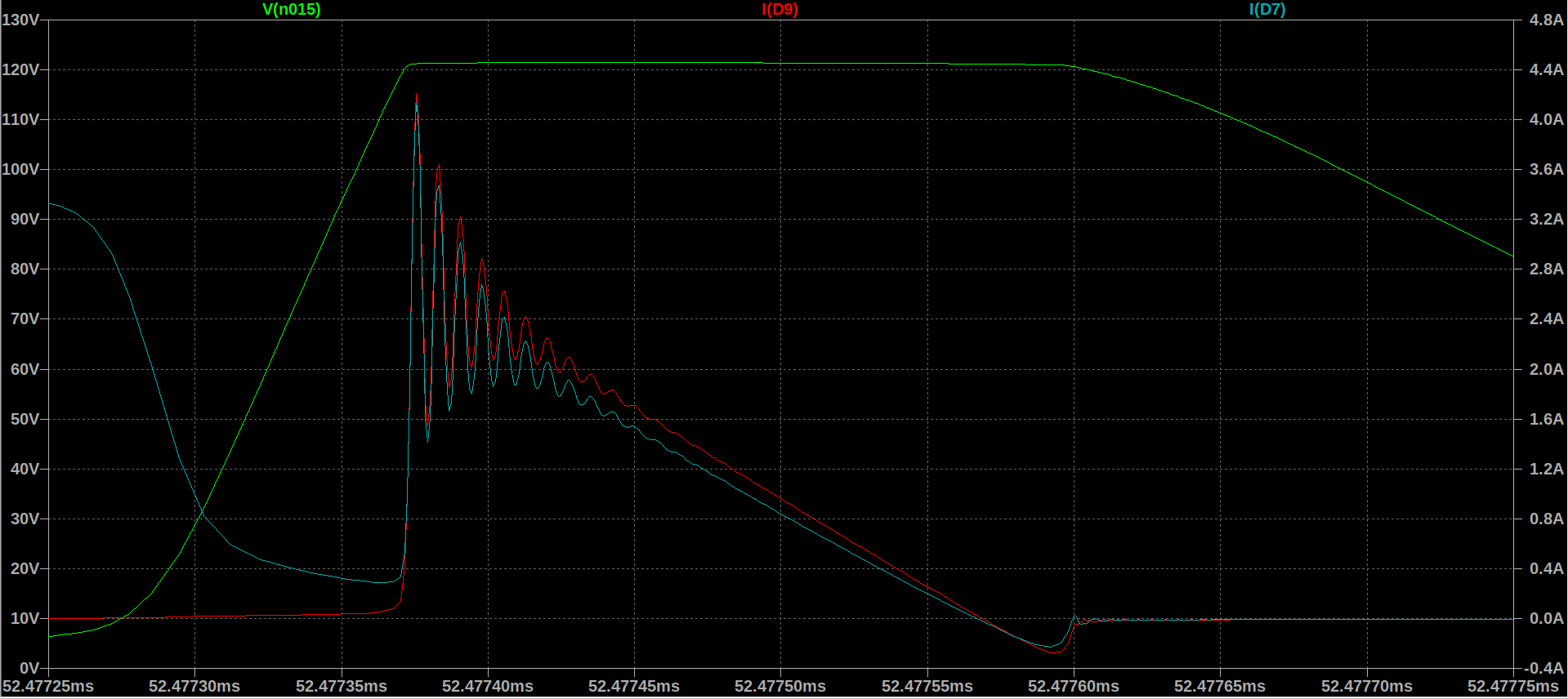

そこでそのサージ電圧を電源に回生して、サージを抑えるだけでなく効率も上げることができる回路が2スイッチコンバータになります。  こんな感じで、一次側の+側にもう一つMOSFETを付け加えて、一次側端子から反対側の電源にダイオードでクランプされた回路となります。フルブリッジ回路から2つのMOSFETをダイオードに置き換えた回路と見ることもできます。 動作ですが 1.電源からMOSFETを通じてトランスコアにエネルギーが蓄えられます。  2.二次側の放電と同時に一次側に発生したサージがダイオードを通じて電源側へ帰ります。このときL1が電源電圧にクランプされてサージ電圧が低下します。  このような動作が繰り返されます。 これで余分なサージが電源側に回生されるので同時に効率も上げることができる一石二鳥な回路となります。 ++ちなみこの2スイッチ回路、フォワードコンバータにも使うことができます。++ シミュレート - 前回の回路を少しだけ改良したものがこちらになります。  前回の回路に加えてハイサイド側を追加したり、電源を交流にしてみました。  赤のV(vh)が電源電圧で、緑のV(n015)がローサイドのM1ドレイン側,青のV(n009)がハイサイドのM2ソース電圧になります。どちらのFETに発生するサージ電圧の最大値が電源電圧付近で頭打ちになってるのがわかります。  ローサイドM1のMOSFETがオフになってドレイン電圧が上昇したときにD7とD9に三角派に近い電流が流れて、サージが電源に回生されているのがわかります。(それ以前にD9に電流が流れていますがそこは無視してください) このときのM1のドレインに発生するサージ電圧は $${V_{surge}=V_{H}+V_{F_9}}$$ つまり電源電圧VHにD9の順方向電圧VF9が重畳された電圧になります。おそらく配線の浮遊インダクタンスなどによってもう少し上昇すると思いますが、MOSFETの耐圧もこの電圧付近まで下げることが可能となります。