lyricalmagical が 2025年02月02日00時59分09秒 に編集

初版

タイトルの変更

CMOSレベルで論理回路やメモリを設計してみる

タグの変更

CMOS

記事種類の変更

製作品

ライセンスの変更

(CC BY-NC 4+) Creative Commons Attribution-NonCommercial CC BY-NC version 4.0 or later

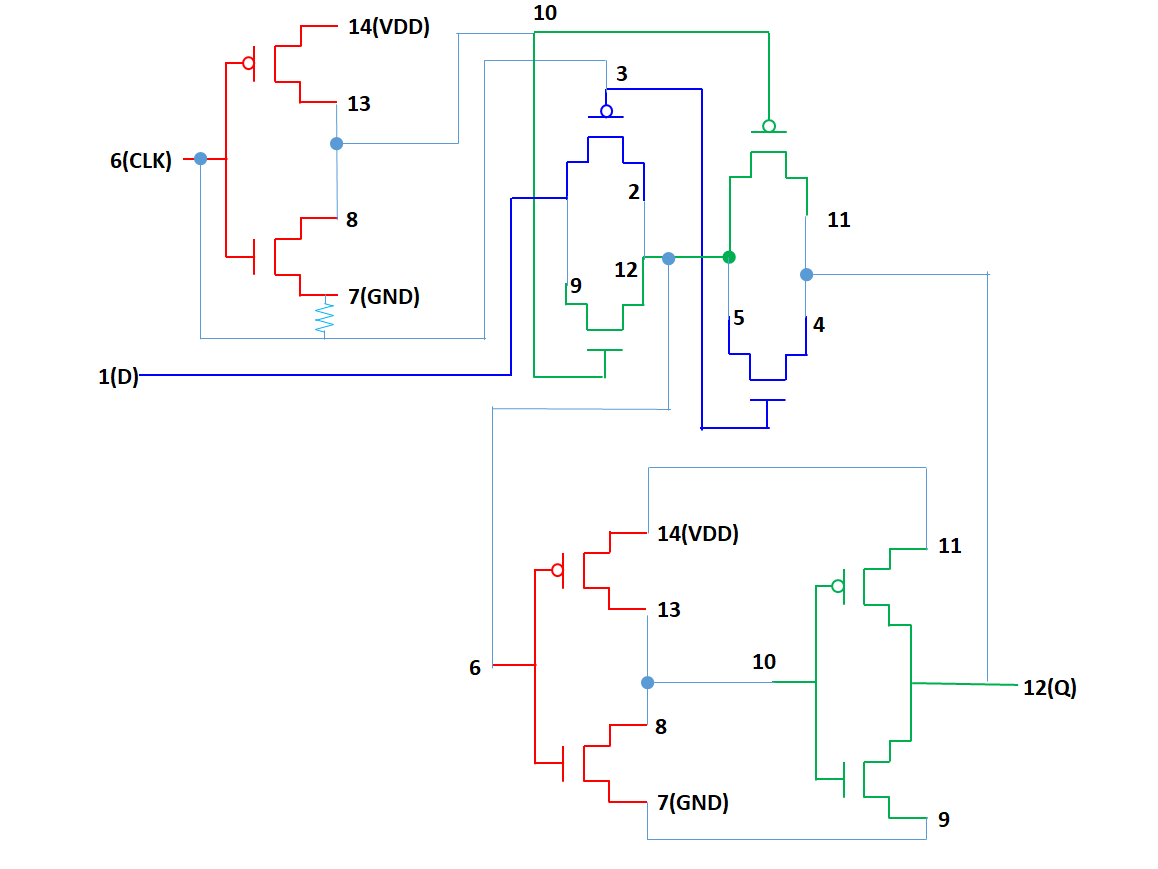

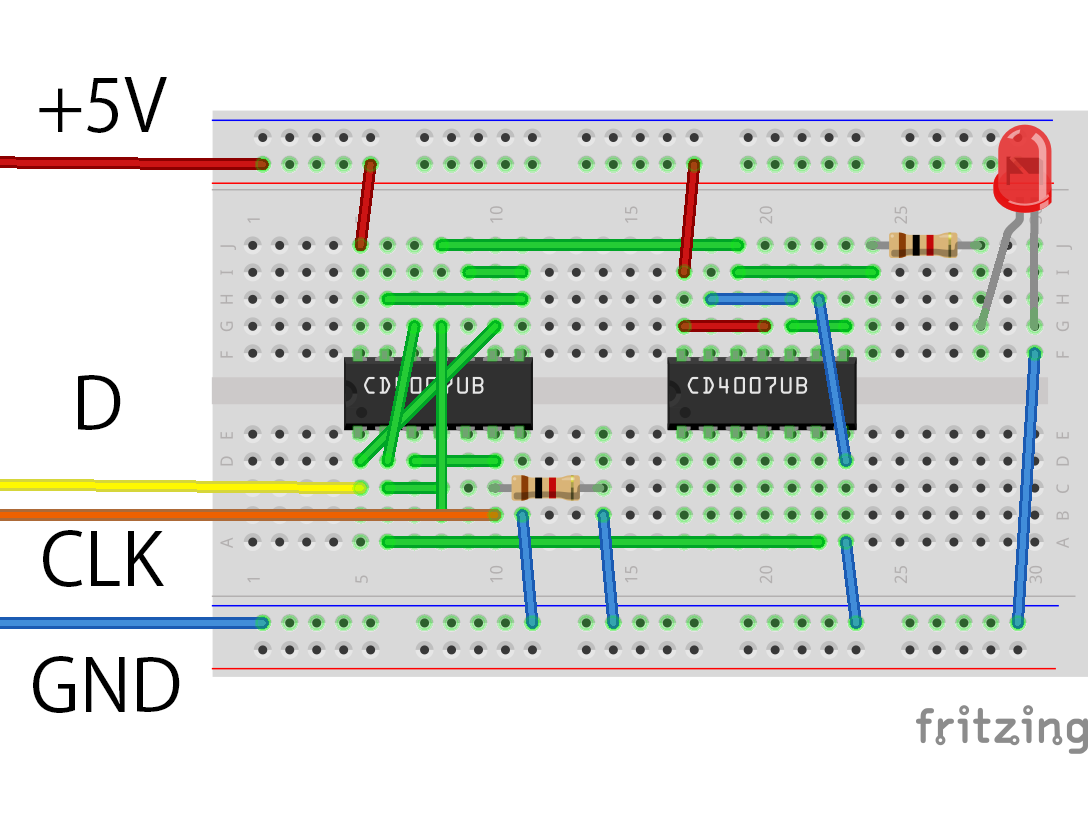

本文の変更

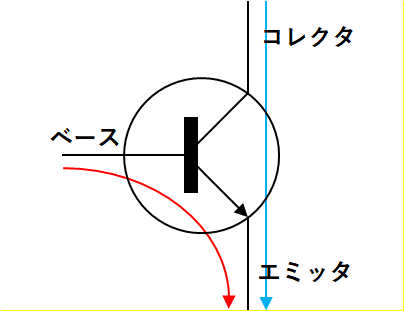

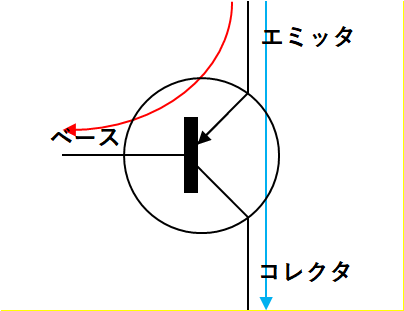

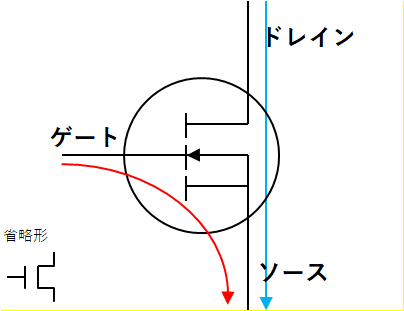

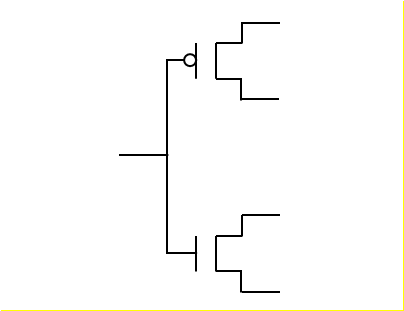

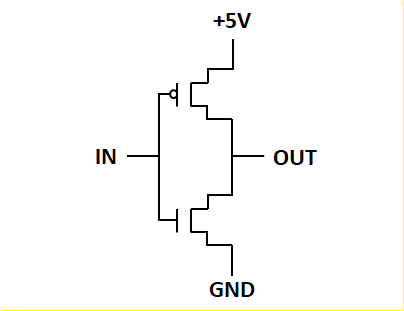

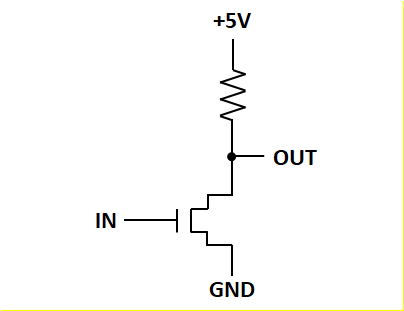

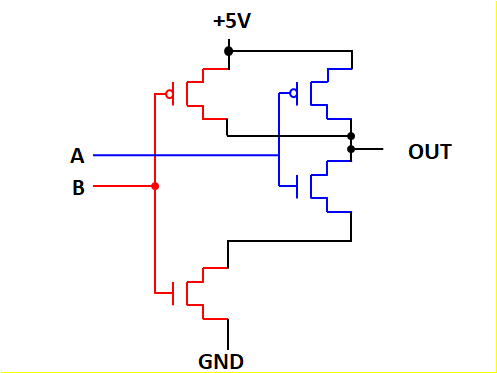

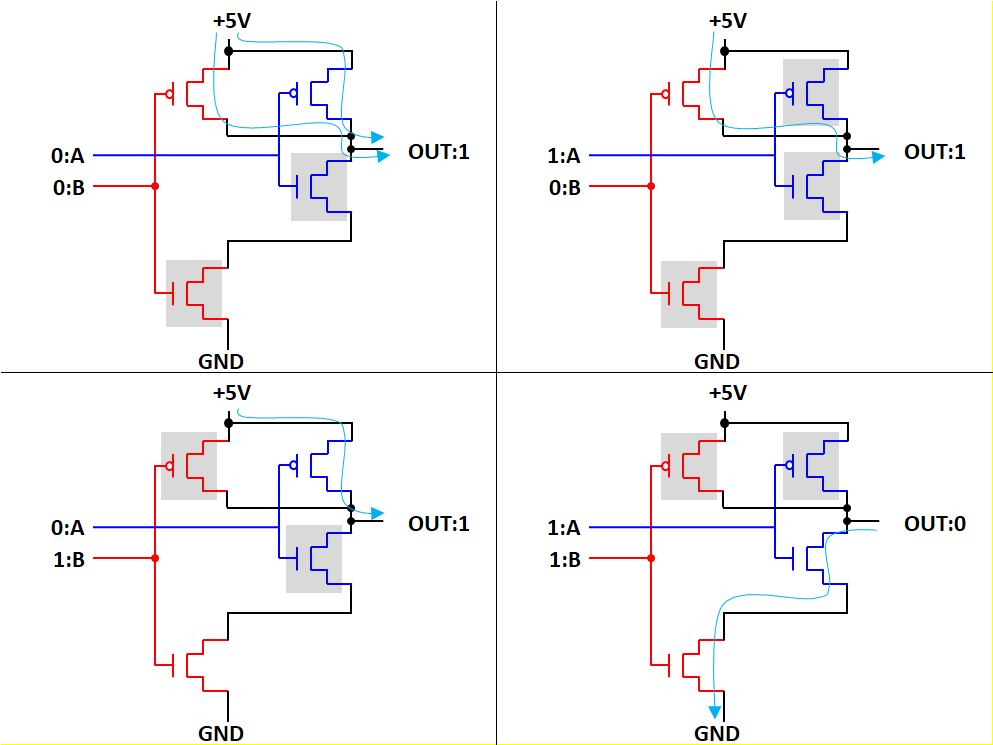

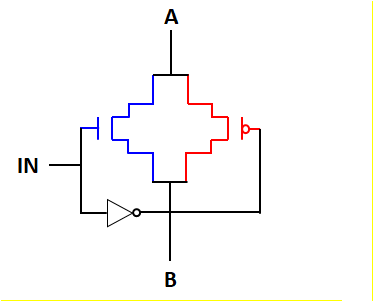

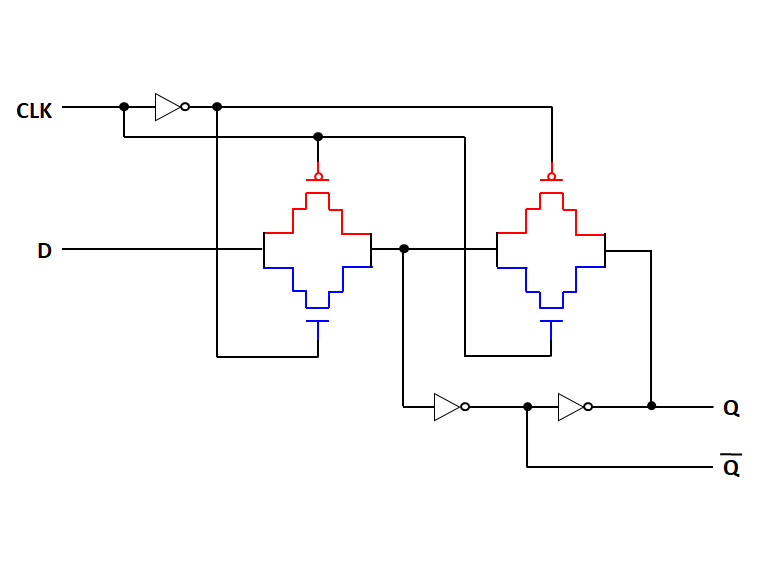

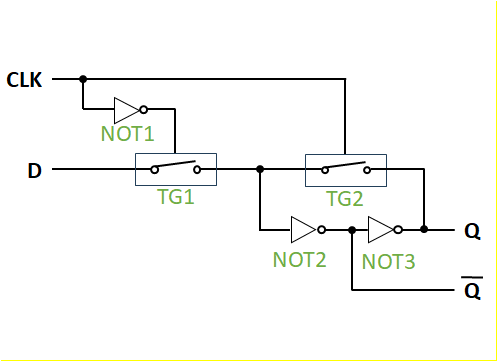

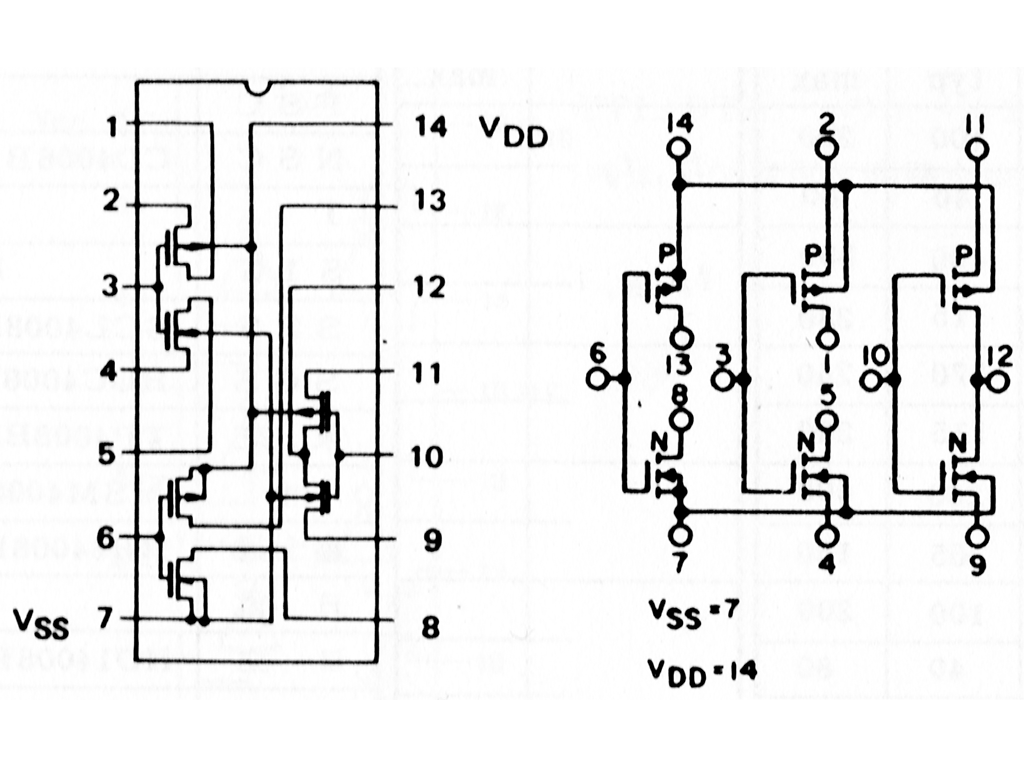

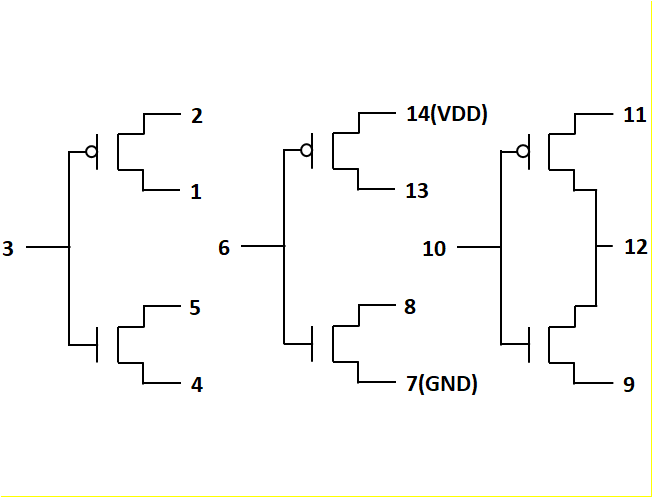

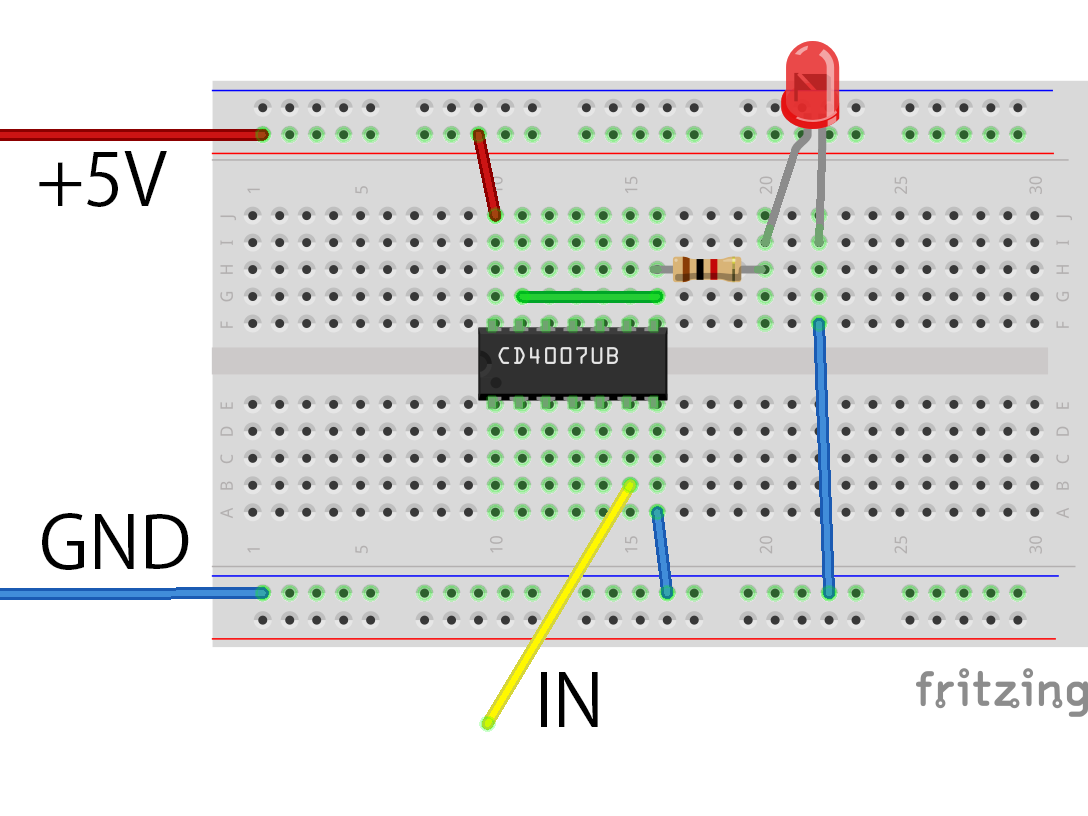

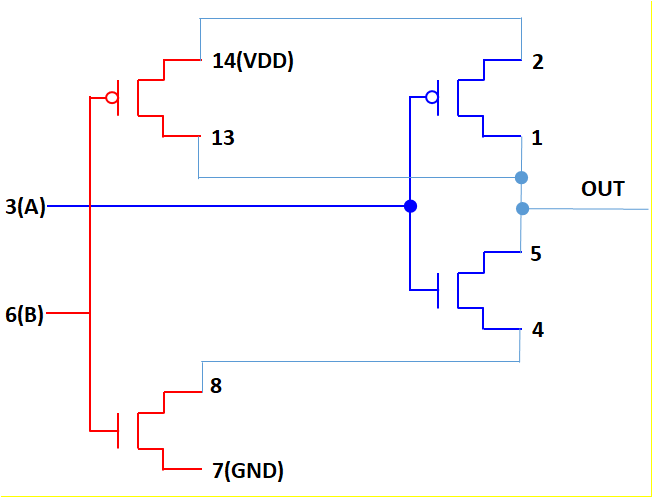

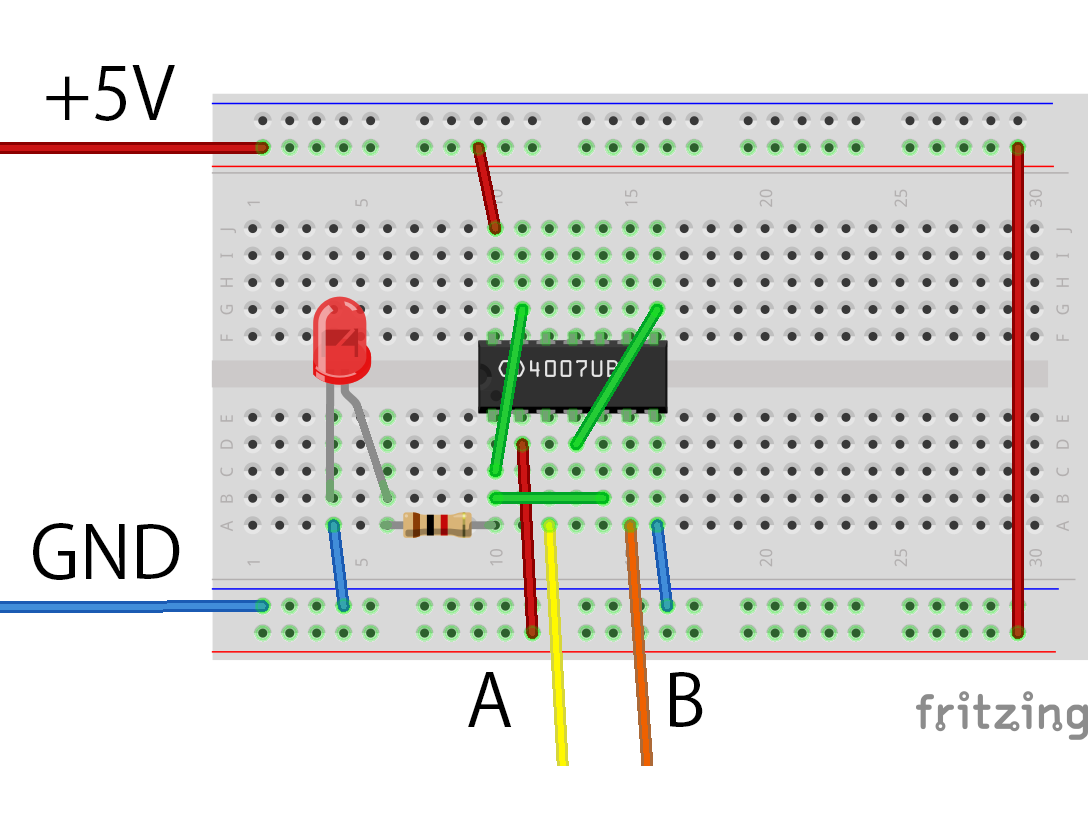

## CMOSの概要 近年のデジタル回路の構成要素であるLSIなどは、ほぼCMOS構成で作成されています。CMOSが主流になる前(1980年代頃)はNMOSが主流で、さらにそれ以前はTTLが主流でした。この記事ではNMOS/TTLについてはほぼ触れません。 CMOSはComplementary MOSの略称で、MOSが2つセットになったものです。 ではMOSとは何かですが、これはMetal Oxide Semiconductorの略ですが、FETの一種です。 FETはField Effect Transistorの略で、その名の通りトランジスタの一種です。 ※MOSではないFETも存在しますが省略します。 まず、超ざっくりこれらの動作について、CMOS回路を理解するために最低限必要なレベルで説明します。 ※ちなみにPC用語で(一般的にBIOSの設定クリアなどと一緒に使われる)CMOSという用語は別物、というか誤用です。データの保持用の部品がCMOS構成で作成されていたため、CMOSと呼ばれるようになったらしいです。 ### (バイポーラ)トランジスタ ここでいうトランジスタは、Field Effectではないトランジスタです。 あえてFETと区別するときは、バイポーラ型トランジスタ(以下BPトランジスタ)といいます。 トランジスタには大きく分けてNPN型とPNP型の2つが存在します。一般的なのはNPN型です。といってもどちらも珍しいものではなく、現実的にはどちらが一般的ということはありません。 それでもなおNPN型が一般的となるのは、「真空管の動作に似ているため過去の考え方を踏襲できる」「PNP型よりちょっと特性が良い場合がおおいので、どちらでもよい場合はNPNを使ったほうが良い」というあたりがあるようです。 2SAや2SBで始まる型番がPNP型、2SCや2SDで始まるものがNPN型です(それ以外の型番のトランジスタもありますが詳細はデータシートなどを参照してください)。 #### NPNトランジスタ  極めて一般的なトランジスタです。みんな大好き2SC1815などです。 ベース→エミッタ(図中赤線)に微小な電流を流すと、コレクタ→エミッタ間(図中青線)に大きな電流が流れます。 つまり、単方向のスイッチのような動きをします。 ベース→エミッタに流れる電流によりコレクタ→エミッタに流れる電流も変わるため、このあたりをいい感じになるように設計するとアナログ増幅ができますが、CMOS回路を理解する上ではここまで複雑な動作は必要ないため、とりあえずはスイッチという理解で問題ありません。 #### PNPトランジスタ  動作としてはNPNと同じですが、電流が流れる方向が逆になります。エミッタ→ベース(図中赤線)に微小な電流を流すと、エミッタ→コレクタ(図中青線)に大きな電流が流れます。 つまり、NPN/PNPどちらの場合も、コレクタ←→エミッタ間に電流を流す(スイッチをONする)ためには、ベース←→エミッタ間に電流を流し続ける必要があります。結果、「スイッチをONするための電流(=電力)」が必要となるため、スイッチをONしている間は仮にスイッチ本体に電流が流れていなくても消費電力が発生します(電磁石式リレーと同様。ここ重要)。 ### FET こちらもBPトランジスタのNPN/PNPに相当する、NchFET/PchFETが存在します。 BPトランジスタと似たような動作をしますが、端子の名前が異なり、ゲートがベース、ソースが エミッタ、ドレインがコレクタという関係になります。 #### NchFET  ゲート→ソース間(図中赤線)に電位差(ゲートが+)があると、ドレイン→ソース間(図中青線)に電流が流せるようになります。 矢印の向きが逆っぽい気がしますがこういうものです。 BPトランジスタと異なる点は、ゲート→ソース間に「電位差」があるだけでよく、「電流」を流す必要がないため、理論上はスイッチをONするための電力というのが不要になります。 ※FETの回路記号は種類により微妙に異なるものがあります。また、(特にCMOSの場合)省略形として左下の記号を使うことがあります。以降省略形で記載します。 #### PchFET  こちらも動作としてはNchと同様ですが、電位差や電流の向きが逆になります。ゲート→ソース間(図中赤線)に電位差(ソースが+)があると、ソース→ドレイン間に電流が流せるようになります。 ### CMOS CMOSとは、NchFETとPchFETを下記のようにゲートを共通につなげたものになります(なので、章立てとしてここにあるのは少しおかしいです)。  この組み合わせの端子をいろいろ接続することで、いろいろな論理回路を作ることができます。 ## 具体的なCMOS回路例 ここではLレベルを0V、Hレベルを5Vとして表記します。 ### NOT 最も簡単なNOT(invert)回路をCMOSで記載してみます。CMOS1ペアで作成できます。  INが0Vの場合、PchFETのソース→ゲート間に電位差があるため、スイッチがONとなり、+5VとOUTが接続された状態になります。また、NchFETはソース→ゲート間に電位差がないためOFFとなってますので、GNDとOUTは接続されません。結果、OUTは+5Vだけと接続された状態になり、OUTには5Vが出力されます。 INが5Vの場合、今とは逆の動作となり、PchFETがOFF、NchFETがONとなり、GNDとOUTが接続された状態になります。 どちらの場合も、電位差(電圧)のみでスイッチのON/OFFが決まるため、理論上消費電力は0になります。 また、参考までにNMOSの動作も記載します。  INが0Vの場合、NchFETはOFFとなりますので、+5Vは抵抗を介してOUTに接続された状態となり、OUTには約5Vが出力されます。 INが5Vの場合、NchFETがONとなりますので、OUTはGNDに接続され、OUTはVとなります。ただし、この場合、抵抗には定常的に電流が流れ続けるため、MOS FETを使用した場合でも消費電力が発生します。 また、回路図は省略しますが、FETではなくトランジスタを使った場合(TTL時代)、スイッチをONするためのベース→エミッタ間にも電流が流れるため、さらに消費電力が増加します。これがTTL>NMOS>CMOSと消費電力が少なくなる理由です。 ### NAND 次にNANDを設計します。CMOS2ペアで作成できます。 ちなみにORやANDは2ペアでは作成できないため、NANDがNOTに次いで簡単な回路となります。  これだけ見てもぱっと見では実際どのように動くのかわかりにくいので、入力4パターンすべての時の動作を図示してみました。 グレーハッチされているMOSがスイッチOFF状態となっているものです。 水色の経路の接続がつながり、OUTには想定通りの出力が得られることになります。  ### メモリ NOTとNANDが作れると、基本的に組み合わせ回路はなんでも作れます。全加算器なども頑張れば作れます。 ただし、メモリについてはトランスファゲートという別の考え方が必要です。 ※メモリの回路構成というと、NAND回路をたすき掛けしたような回路例が多く出てきますが、トランスファゲートを使用した構成のほうが回路規模の点で有利なため、実物ではNAND構成の採用例は少ないはずです。 ここではDラッチを作ってみますが、その前にトランスファゲートの説明をします。 #### トランスファゲート  図中にNOT記号がありますが、回路図簡略化のためこのように記載しています。実際の中身は前述のNOT回路になります。 さて今までの説明では触れていませんが、FET(MOS)の物理的な構造について少し触れておきます。 トランジスタ(FET/BPとも)とはP型半導体とN型半導体(それがどういったものかはここでは触れません)を、「NPN」や「PNP」といった形で挟んだ構造になっています。それぞれの半導体部分がそれぞれドレイン/ゲート/ソースと対応しています。つまり、ゲートをドレインとソースで挟んだ構造です。 そのため、最も単純な構造では、構造上ドレインとソースに差異はありません。しかし、実際の単体FETパーツではバックゲートというものが存在し、ドレインとソースの極性が決まっています。バックゲートについてはここでは触れません。基本的な構造としてはドレインとソースに区別はないということをまず把握してください。 なので、実際にはNchMOSの動作としては、P極(ゲート電位)がN極(ドレインもしくはソース)より高ければ、N極から反対側のN極まで導通状態になります。PchMOSではその逆となります。 それを踏まえてトランスファゲートの回路を見ると、 INが0Vのとき、NMOS(左側:青で記載されたMOS)はゲート電位がAやBよりも高いことはあり得ない、導通状態になりません。 また、PMOS(右側:赤)はINVを挟んでいるため、ゲート電位がAやBより高いため、こちらも導通状態にはなりません。 INが5Vのとき、NMOSは、ゲート電位がAやBよりも高いため導通状態となり、A/Bいずれかの0Vが反対側に伝搬することとなります(片方は0V入力、反対側は0V出力となる)。 また、PMOSは、ゲート電位がAやBよりも低いため導通状態となり、A/Bいずれかの5Vが反対側に伝搬することとなります(片方は5V入力、反対側は5V出力となる)。 つまり、INがLの時は非疎通、INがHの時は双方向に信号が伝搬するスイッチとなります。 このように、トランスファゲートは向かい合った一組のCMOSと、そのほかに1つのNOTで構成されます。 #### Dラッチ  計5セットのCMOSで構成されています。トランスファゲートが2つになり、さらにわけわからなくなりましたね。 また、前述のトランスファゲートの説明では、向かい合ったCMOSとNOTで構成されると記載しましたが、2つのトランスファゲートのNOTは共用化されて一つになっています(図中左側のCLK線にあるNOT)。 なので、わかりにくいため、トランスファゲートを単純化して、「HでONとなるスイッチ」として書き直します。  だいぶシンプルになりました。それでは動作を考えましょう。 ・CLK入力がLのとき TG1がCLOSE状態となるので、D入力の値がNOT2に入力され、NOT3を経由してQ出力に反映されます。そのため、D入力はそのままQ出力に反映されます。 ・CLK入力がHのとき TG1はOPEN状態になるので、D入力はどこにも反映されません。 TG2はCLOSE状態となるため、現在のQ出力の値(=NOT3の出力)はTG2を経由してNOT2に再び入力されるため、NOT2→NOT3→TG2の中で信号がぐるぐると回り続け、先ほど(CLK入力がLのとき)までQに出力していた値を保持し続けることになります。 このようにして、ラッチ回路(1bitメモリ)は構成されます。 ちなみにラッチ/フリップフロップ系では、Q出力のほかに、Qの反転出力があることが多いですが、用途が多いから反転回路をつけているというわけではなく、内部的にもともと反転した状態を持っているため、ついでに外に出しておいたということになります。反転出力をつけることで回路規模が大きくなるということはありません。 ## 作ってみる これを実際に作って動作を確認してみます。CMOS4000シリーズというICがありますが、そのうちの4007というものに、CMOSが3つ入った単純なものがあります。これを使用して実験してみます。 端子配置とブロック図はこのようになっています。わかりやすくCMOSが3組入っています。  いまいちわかりにくいので3つに分離して記載します。  ちなみに、先ほどちらっと説明に出たバックゲートの関連で、MOSFETにはゲート/ソース/ドレインのほかに実際には電源が必要です。 14pinと7pinは電源と共用ですので、ここの接続は変更できません。 ### NOT ブロック図中の一番右は元々NOTとして使用できますが、せっかくなので別の箇所を使って作ってみましょう。 ブロック図中の真ん中(ゲートが6pin)を使うのが配線量が少なく便利そうです。  左側の+5VとGNDには電源を接続します。 動かしてみた様子がこちらになります @[youtube](https://youtu.be/q7itMy73cDU) INを5VにつなぐとLEDが消灯し、GNDにつなぐとLEDが点灯しますので、NOT動作が確認できました。 ※入力が5VにもGNDにもつながっていないときは、状態は不安定になります。この動画では数Hzで点滅しているように見えていますが、実際にはかなり高速に点滅していました。本来CMOSではこのように入力浮き状態となるような回路を作成してはいけません。 ### NAND いきなりブレッドボード上で配線しようとしてもわからなくなるので、いったん結線図を前述の回路図に合わせてわかりやすく書いてみます。  細い青線がICの外の配線となりますので、この通りブレッドボード上で配線します。 左側の+5VとGNDには電源を接続します。  動かしてみた様子がこちらになります @[youtube](https://youtu.be/I03NnGg8AaE) AとBをそれぞれ5VもしくはGNDにつなぐことで、NAND動作を見ることができます。 AとB両方を5Vに接続した場合のみ、LEDが消灯しますので、ただしくNAND動作していることが確認できました。 ### Dラッチ CMOSが5組なので、ICを二つ使います。 こちらもいったん回路図を考えてみます。  なるべく元のCMOS構成の回路図のイメージを残すように書いてみました。上下でICが分かれています。 CLKとGNDの間にプルダウン抵抗がありますが、CLKをオープン(HでもLでもない状態)にすると回路動作に問題が起きる可能性があるため追加しています(前のほうにも書きましたが、基本的にCMOSの入力はオープンにしてはいけません)。 これをブレッドボードで配線するのは結構つらい気もしますが頑張ってみます。  動かしてみた様子がこちらになります @[youtube](https://youtu.be/9Omen0AHOkU) CLKをL(GND)に接続した場合、D入力の値がLEDに反映され、CLKをH(+5V)に接続した場合はD入力に関係なく値が保持されていることが確認できます。 ## おわりに CMOS動作の理論としては知っているものの、実際にこのようにMOSレベルで動作確認したことはありませんでしたので想定通り動作してくれてよかったです。 特にラッチ回路はタイミング的に動作するかも不明でした。 動作の解説などではNANDなどの組み合わせで説明されることが多いラッチ系回路ですが、実際にはトランスファゲートを使用することで回路規模を削減することができます。 また、全加算器もトランスファゲートを使用することで回路規模を削減することができます。 このような実際の回路を知っておくことで、何かの役に立つこともあるかもしれません。まあなさそうですが…。 ## 参考サイト バイポーラトランジスタの種類と使い方 https://techweb.rohm.co.jp/trend/glossary/16543/ 「CD4007」を使って様々なロジック機能を実現する https://www.analog.com/jp/resources/analog-dialogue/studentzone/studentzone-september-2022.html CMOSベースのDラッチ回路 https://www.analog.com/jp/resources/analog-dialogue/studentzone/november-2022.html CD4007UB TYPES データシート https://www.ti.com/jp/lit/gpn/cd4007ub