mikecat が 2022年12月06日23時28分41秒 に編集

初版

タイトルの変更

Kageki (TD4互換機) でロータリーエンコーダを読み取る

タグの変更

Kageki

TD4

ロータリーエンコーダ

アセンブリ

メイン画像の変更

記事種類の変更

製作品

ライセンスの変更

(CC BY 4+) Creative Commons Attribution CC BY version 4.0 or later

本文の変更

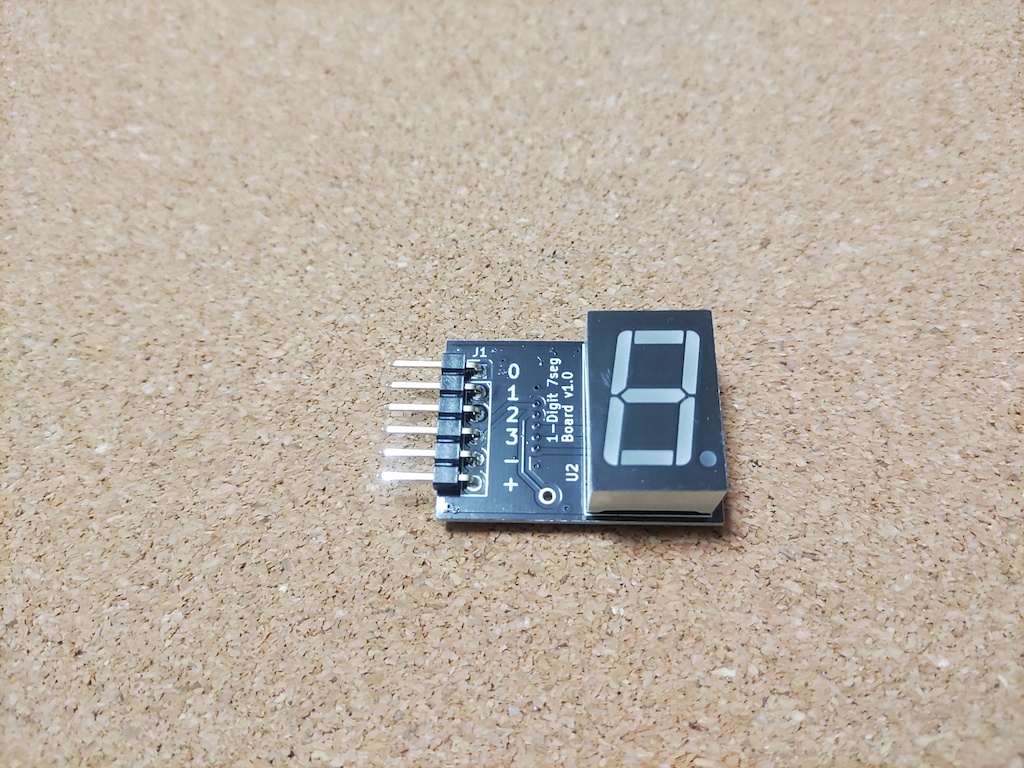

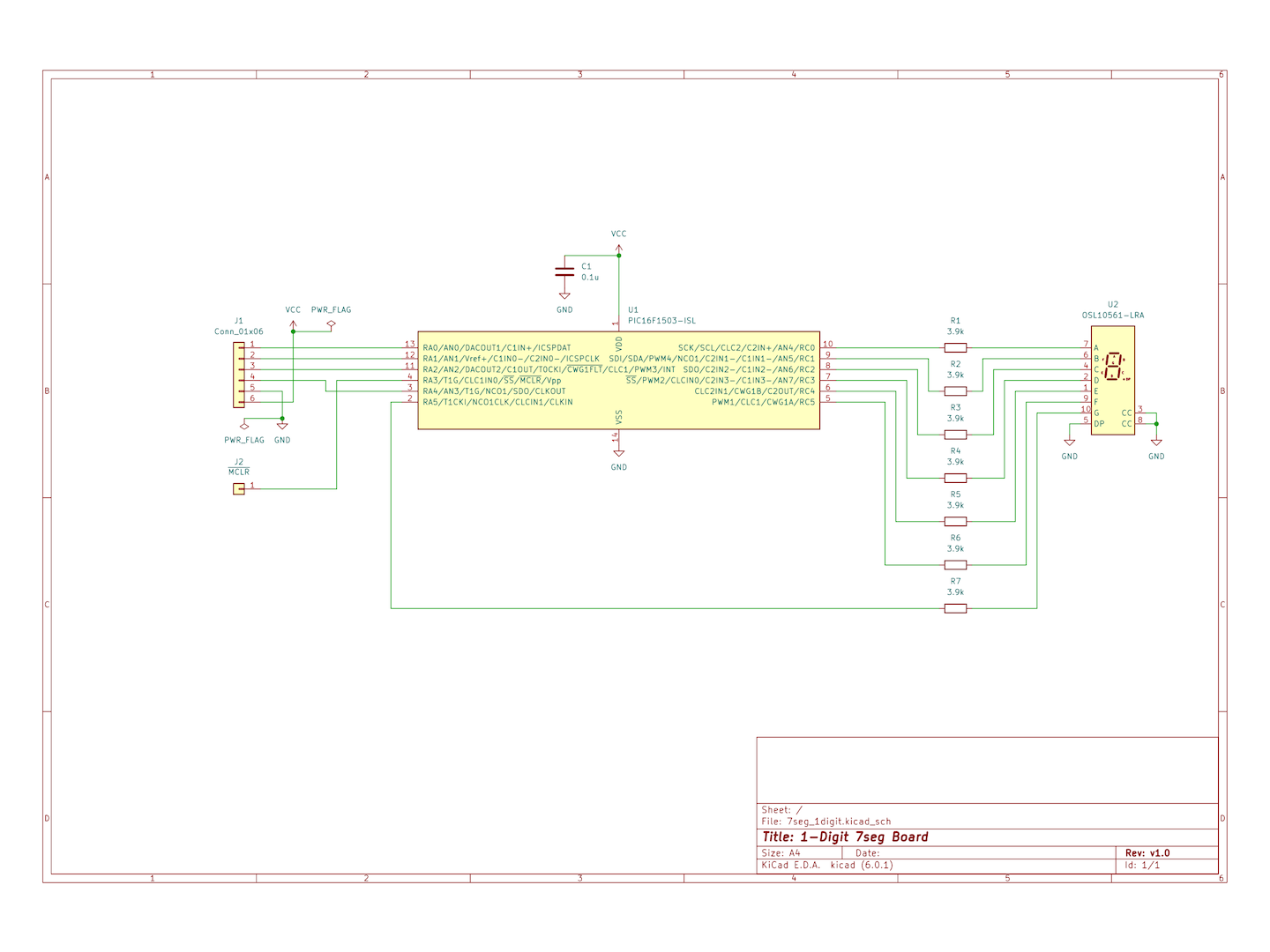

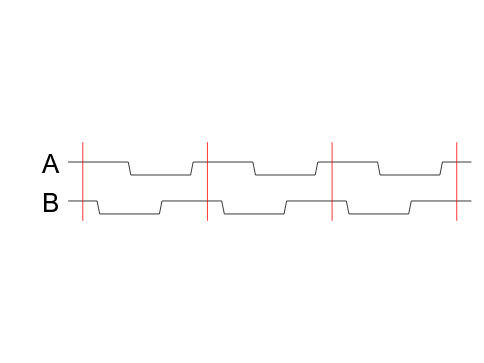

++[自作CPU Advent Calendar 2022](https://qiita.com/advent-calendar/2022/diycpu) 6日目++ [TD4の命令を実行できる自作CPU「Kageki」](https://elchika.com/article/9ac9fd67-86c5-4b1b-a355-4f662e8af794/) でロータリーエンコーダの入力を読み取ってみた。 今回は、ロータリーエンコーダとして [Pmod ENC](https://digilent.com/shop/pmod-enc-rotary-encoder/) モジュールを用いた。 # 1-Digit 7seg Board ||| |---|---| [基板設計データ](https://github.com/mikecat/hardware_cpu/releases/tag/20221008-boards-v1.0) | [ソフトウェア](https://github.com/mikecat/hardware_cpu/tree/main/software/io/7seg_1digit) 4ビットの入力値を16進数1桁で表示する。 # ロータリーエンコーダ (今回扱う)ロータリーエンコーダは、軸の回転の情報をA,Bの2本の信号がずれたタイミングで切り替わることで伝えてくれるデバイスである。 Pmod ENC では、A,BともにHIGHの状態で安定し、次の安定する場所まで軸を動かすとA,Bがそれぞれ2回ずつ (計4回) 切り替わって再びともにHIGHの状態になる。 例えば、軸を上から見て時計回りに回転させると、以下のような信号が得られる。  # 実装 今回は、A,BがともにHIGHの状態から、AまたはBが立ち下がるタイミングに注目して検出することにした。 以下が、今回実装したプログラムである。 ``` 位置 機械語 アセンブリ言語 ---------------------------------- 0 00100000 START: IN A 1 00000100 ADD A, 0100 2 11100100 JNC JUDGE_2 3 11110000 JMP START 4 00000100 JUDGE_2: ADD A, 0100 5 11101000 JNC JUDGE_1 6 01011111 ADD B, 1111 7 11111011 JMP OUTPUT 8 00000100 JUDGE_1: ADD A, 0100 9 11100000 JNC START A 01010001 ADD B, 0001 B 10010000 OUTPUT: OUT B C 00100000 WAIT: IN A D 0 000100 ADD A, 0100 E 11101100 JNC WAIT F 11110000 JMP START ``` 入力ポートの2ビット目 (0-origin) に Pmod ENC の A を、3ビット目に B を接続して実行する。 ※Pmod ENC をそのまま入力ポートに挿すと A は0ビット目、B は1ビット目となるので、ケーブル (など) を用いる 0~3番地で、A,BがともにHIGHの間待機する。 4~7番地で、A(のみ)が立ち下がったかを判定し、もしそうであれば出力する値をデクリメントする。 8~A番地で、B(のみ)が立ち下がったかを判定し、もしそうであれば出力する値をインクリメントする。 B番地で、新しい値を出力する。 C~E番地で、A,BがともにHIGHに戻るまで待機する。 F番地で、最初の待機に戻る。 # 実行結果 出力ポートに 1-Digit 7seg Board を接続し、実行してみた。 @[youtube](https://www.youtube.com/watch?v=IiMNEz854zc) 以下のような実行結果になった。 |クロックの速度|実行結果| |---|---| |1Hz|中途半端に回した状態で待てば、一応検出させることができる| |10Hz|ゆっくり回せば、検出させることができる| |100Hz|だいたい快適に動くが、意図しない戻りも発生する| |1kHz|快適に動く|