GowinのOSER10検証 その1 から派生して、2 種類のロジックアナライザの性能を比較してみます。オシロスコープで観測した波形とロジアナの波形を比較しながらそれぞれのロジアナの特徴を見ていきます。

使用するロジックアナライザの紹介

1 つ目の DreamSourceLab DSLogic Plus は最高サンプリングレート 400MHz。付属の測定ケーブル(シールド有り)を使います。

2 つ目の ALIENTEK DL16 Plus は最高サンプリングレート 1GHz。つい先日買いました。付属の測定ケーブル(シールド無しの被覆導線)を使います。

まずはオシロスコープで観測

ロジックアナライザで見える波形がどの程度信用できるのかを判断するのに、オシロスコープでアナログ波形も見ておきたいと思います。オシロスコープで見えた波形が完璧に正しいわけでもありませんが、参考にはなるでしょう。

fclk=189MHz とし、テレダイン・レクロイの WavePro 950 で波形を観測してみます。チャンネル設定は次の通りです。

- CH1: fclk(189MHz のクロック)

- CH2: pclk(189MHz/5 = 37.8MHz のクロック)

- CH3: oser_out(OSER10 の出力、fclk の両エッジに同期して変化)

- CH4: OSER10 のリセット信号

定常波形

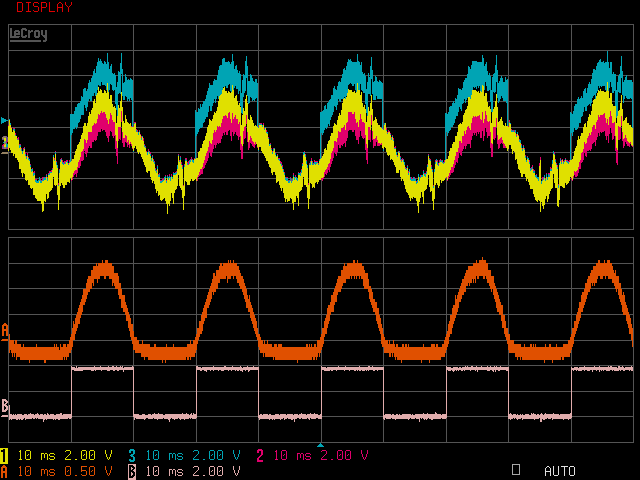

まずは FPGA に電源を入れてしばらく時間が経ったときの波形を見てみます。

パッシブプローブを使っているからか、あるいは FPGA の出力端子の性能限界だからか、波形が大分なまっています。まあでも、とりあえずタイミングを見る用途なら参考になりそうです。

2V のところに補助線(紫)を引き、oser_out の論理値を確認してみます。

1001000111 と読めました。位相をずらせば 1000111100 となり、これは OSER10 に入力している 10 ビットデータ 10'b00_1111_0001 を LSB から順に出力したものと一致します。

ちなみに CH1(fclk)は 5 周期分で 26.4ns ですから、1 周期は 5.28ns であり、周波数は 189.4MHz と計算できます。理論値は 189MHz なので、ほぼ正確です。

リセット解除時の波形

次に、リセット解除後にどのような波形になるかを観測します。

CH2(pclk)でトリガがかかってからしばらくして CH4(OSER10 のリセット信号)が立ち上がっています。これは意図した遅延です。pclk の立ち上がりと OSER10 のリセットをずらしたときの挙動を調べるために、わざと fclk の 1 周期分、OSER10 のリセットを遅らせているのです。

CH4 の立ち上がりは CH2 の立ち上がりから 5ns ほど遅れているでしょうか。この間に CH1(fclk)がほぼ 1 周しています。意図通りの遅れ量ですね。

DC レベルの変化

リセット解除後の DC レベル(電圧の平均値)の変化を見てみます。

CH2(pclk)および CH3(oser_out)の平均値が、リセット解除後 30μs の間、徐々に上がっています。これは、pclk および oser_out の出力端子には DC 成分をカットするためのコンデンサが接続されているため、その影響でしょう。詳しくは Tang Nano 9K - Sipeed Wiki に載っている FPGA ボードの回路図を参照してください。

OSER10 出力の開始

CH2(pclk)のリセット解除後、どのくらいで CH3(oser_out)が出力されてくるかを見ます。

時間軸を 20ns/div に変更して観測すると、リセット解除後、約 60ns 後に oser_out が出力され始めている感じです。ただ、定常波形では oser_out は 3V を超える部分まで振幅がありましたが、リセット解除直後は 2V を少し超える程度までしかありません。ここから 30μs 程度を経て DC レベルが定常状態になるということです。

ロジックアナライザで観測

各波形のアナログ的な特徴が分かったところで、ロジックアナライザでの観測を行います。これまで見てきたアナログ波形が、ロジックアナライザによりどのように切り取られるでしょうか。

fclk=189MHz ですから、サンプリングレート 400MHz の DSLogic でもそれなりの波形が見えることが期待されます。

ロジックアナライザの閾値(スレッショルド。この電圧より高いと 1、低いと 0 と認識する)は 2V に設定しています。

定常波形

まずは DSLogic Plus での観測波形を示します。

DSLogic は fclk に時々歯抜けがあります。pclk はほぼ正確ですが、分解能 2.5ns の単位にパルス幅が丸められています。

oser_out はどうでしょうか。オシロスコープでは pclk の立ち上がり後から 1001000111 と読めていました。DSLogic では oser_out の波形が定常的な形になっていません。特に、幅 1 のパルスが見えたり見えなかったりしています。

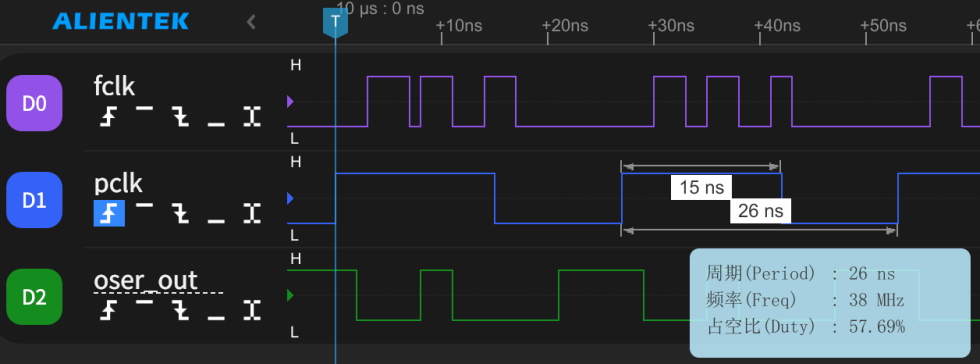

次に DL16 Plus での観測波形を示します。

DS16 は fclk の潰れ方が DSLogic よりひどいです。DL16 のサンプリングレートは DSLogic の 2 倍以上の 1GHz ですし、fclk=189MHz は DL16 Plus の仕様にある Maximum Detectable Frequency 200MHz より低いため、本来は見えるべきなのですが…。プローブが貧弱なのが原因でしょうか。シールドもされてない、単なる被覆導線ですからね。AliExpress にシールド付きケーブルが売られていた ので発注してみました。届いたらこれを使って測定してみたいと思います。

pclk はほぼ正確ですが、アナログ波形での観測より少しデューティ比が低く出ています。

oser_out の波形は定常的な形になっていますし、パルス幅もアナログ波形の観測と一致しています。それなりの正確さで見えてるようですね。

アナログ波形と重ねてみる

DL16 の波形とオシロスコープで見た波形を重ねて、両者が一致するかを見てみます。ただし、両者の波形の取得タイミングは異なる(オシロスコープとロジックアナライザをつなぎ替えて 2 回取得しています)ため、本当に同一の信号を見ているわけではない点には注意が必要です。どちらの波形も定常的な波形なので、ある程度は比較可能だと信じていますが。

オシロスコープの波形に、DL16 の波形を重ねてみました(図の上側)。オシロスコープと DL16 で色設定が異なるので分かりにくくてごめんなさい。波形の対応は次の通りです。

- DL16 の D1(青):オシロスコープの CH2(マゼンタ)

- DL16 の D2(緑):オシロスコープの CH3(シアン)

こう見ると、オシロスコープの波形と DL16 の波形はある程度一致しているなあと思います。DL16 の分解能は 1ns(1GHz)ですから、そもそもアナログ波形とタイミングが完全に一致することはありません。

リセット解除直後

リセット解除直後の様子をロジックアナライザで見てみます。

DSLogic はリセット解除後約 67ns で oser_out が観測され始めています。これは、オシロスコープでの観測事実(リセット解除後 60ns 程度で oser_out が立ち上がった)とほぼ一致します。

ただし、波形は定常状態とは違い、パルス幅が短いです。オシロスコープで見たとおり、リセット解除から 30μs ほどは DC レベルが徐々に上がっていくので、最初は電圧が全体的に低く、ロジックアナライザの閾値設定 2V をなかなか超えないためと考えられます。

DL16 は4.3μs 程度経ってようやく oser_out に信号が出始めています。閾値設定は DSLogic と同様 2V にしているのですが、なぜですかね…?

リセット解除後 4μs 付近

DL16 でやっと波形が出始めるのが 4μs 付近です。

DSLogic では oser_out の幅 1 のパルスは捕捉できていません。

DL16 では とても細いパルスが出るだけで、まったく本来の波形ではありません。

リセット解除後 13μs 付近

このくらいの時間が経てば、DSLogic では幅 1 のパルスが見え始めます。

DL16 では、まだまだパルス幅が本来より短いです。

DL16 はトリガ位置を 1%=10μs としているため、一番上に表示されている時刻(23μs)から 10μs を引くとトリガ位置=リセット解除タイミングからの時間になります。

その後の DL16 での波形

DSLogic はリセット解除後 13μs 付近でもう定常波形に近いものになっていましたが、DL16 はまだまだです。DL16 で oser_out の波形がどう変化するかを追いかけてみます。

リセット解除後 20μs 付近でも、まだパルス幅が短いです。

リセット解除後 40μs 付近で、ほとんど定常波形のパルス幅になりました。

リセット解除後 40μs 付近と 190μs 付近では、あまり違いが分かりません。オシロスコープでの観測より 30μs 程度で DC レベルが安定するので、それを如実に反映した観測結果であるとも言えます。

しかし、定常波形に近い波形になるまでの時間が DSLogic と DL16 でこんなにも違うのは驚きです。DL16 のケーブルが貧弱なのが原因なのでしょうか?

fclk を 371.25MHz とする

fclk を 189MHz から 371.25MHz に変更して観測します。

オシロスコープ

CH2(pclk)の周期が約 13.5ns になりました。約 74.1MHz です。371.25MHz/5 = 74.25MHz なので、ほぼ理論値です。

CH3(oser_out)の波形が凄くでこぼこしています。これは、使用しているプローブの種類と、通常のグランドリードでプロービングしていることが影響していると思われます。

| Ch | 信号 | プローブ名 | プローブ性能 |

|---|---|---|---|

| 1 | fclk | LeCroy PP002 | パッシブ 350MHz |

| 2 | pclk | YOKOGAWA 700998 | パッシブ 400MHz |

| 3 | oser_out | KENWOOD PC-39 | パッシブ 150MHz |

| 4 | OSER10 のリセット信号 | KENWOOD PC-39 | パッシブ 150MHz |

oser_out を見るプローブを変える

PP002 は使用しているオシロスコープと同じメーカーのものなので、最も相性が良いと思います。PP002 で oser_out を見てみようと思います。新しいチャンネル設定は次の通りです。

| Ch | 信号 | プローブ名 | プローブ性能 |

|---|---|---|---|

| 1 | oser_out | LeCroy PP002 | パッシブ 350MHz |

| 2 | pclk | YOKOGAWA 700998 | パッシブ 400MHz |

| 3 | fclk | KENWOOD PC-39 | パッシブ 150MHz |

この設定で定常波形を見てみます。

先ほどまでのシアン(CH3)が、今度から黄色(CH1)になっていることに注意してください。oser_out は 10'b00_1111_0001 を出力しているのですが、幅 1 のパルスが全く見えませんね。

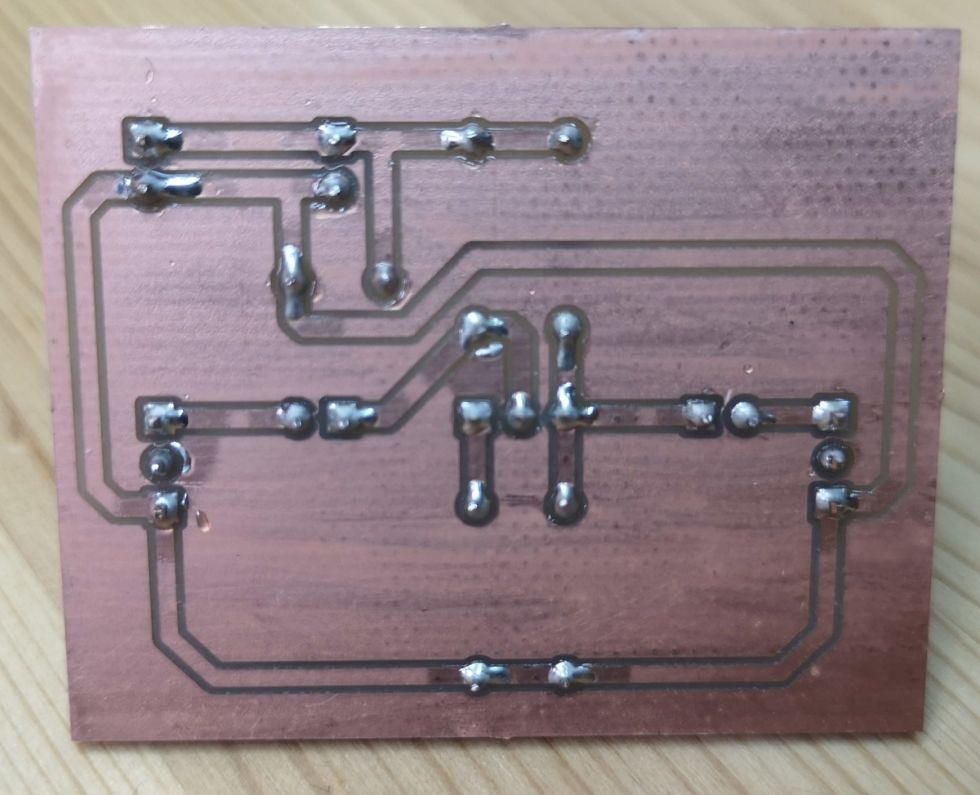

グランドスプリングを用いる

周波数の高い信号を観測する場合にグランドリードを使うと上手く観測出来ません。そこで、試しに CH1 のグランドリードをグランドスプリングに交換して再び観測してみます。さらにフックチップも取り外し、プローブ先端およびグランドスプリングをFPGA ボードの端子に直接接触させました。

fclk=189MHz の際の oser_out は pclk の立ち上がり後から 1001000111 となっていました。CH1 の波形が、なんとなくそうなっているように見えます。補助線を入れてみましょう。

閾値を 2V とすると上手くいかないので、oser_out だけ閾値を 1.5V だとして 1/0 の判定をしました。すると、1001000111 として読めました。実際にこのくらいの速度の通信は差動で送受信すると思います。差動であれば、単純な閾値方式より高い精度で伝送できるはずです。

CH3(fclk)に注目すると、なんだか全体的に波打っています。pclk の周波数の基本波に fclk の周波数の 5 倍波が重なっているような波形です。

DL16

fclk が完全に潰れてしまって見えません。サンプリングレート 1GHz なら 371.25MHz はギリ見えるかなと思ったけどダメでした。この潰れた波形は、もしかしたらオシロスコープで観測した基本波が見えているのでしょうか。

oser_out の波形は安定した形にはなっていますが、幅 1 のパルスが見えなくなりました。幅 1 は 1.35ns 程度なので、最小検出パルス幅が 2ns である DL16 で見えなくても文句は言えません。ケーブルが単なる被覆導線なので、オシロスコープでグランドリードを使った場合のように、パルスが消えてしまっているのだろうと思います。

DSLogic

fclk の潰れ方が DL16 よりひどいです。oser_out の波形も安定しておらず、ひどい形です。分解能 2.5ns のロジックアナライザで 1.35ns とか 2.69ns の幅が観測できないのは仕方ありません。

投稿者の人気記事

-

uchan

さんが

2026/01/15

に

編集

をしました。

(メッセージ: 初版)

ログインしてコメントを投稿する