Gowin IDE の IP Core Generator で生成した UART Master IP の挙動が、Gowin IDE のバージョンアップに伴って変わっています。変化した点を簡単に紹介します。詳細な検証はできていないので、実使用の前にご自分で検証をお願いします。

UART Master IP とは

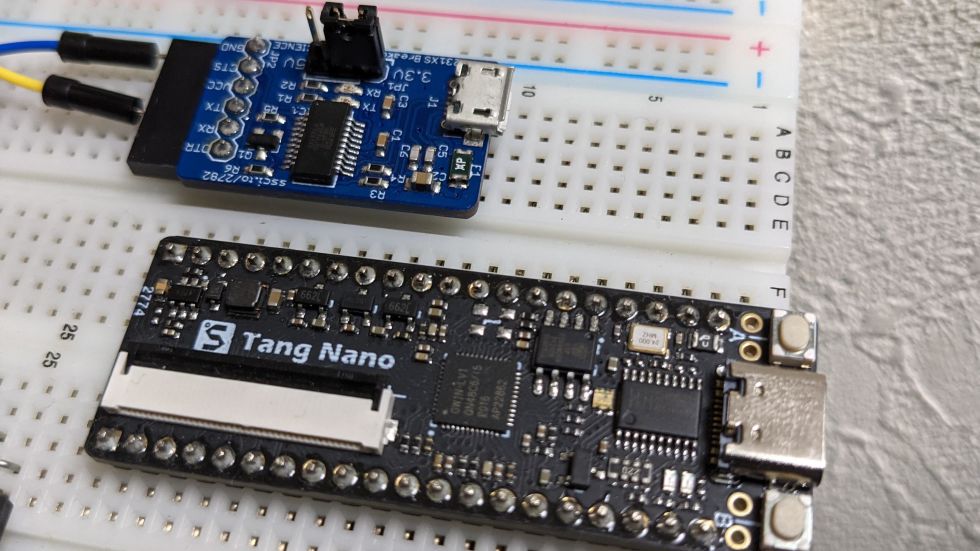

UART(シリアル通信)の送受信を行う IP コア(FPGA メーカーが提供する回路ブロック)です。Gowin IDE の IP Core Generator で生成できます。参考:「Tang NanoでuartのIPコアを動かした件」を読み解く

Gowin IDE と UART Master IP のバージョン対応表:

| Gowin IDE | UART Master IP |

|---|---|

| 1.9.8 (build 54687) | 1.0 |

| 1.9.8.01 (build 55895) | 1.1 |

| 1.9.8.03 (build 56783) | 2.0 |

UART Master IP 1.0 の動作

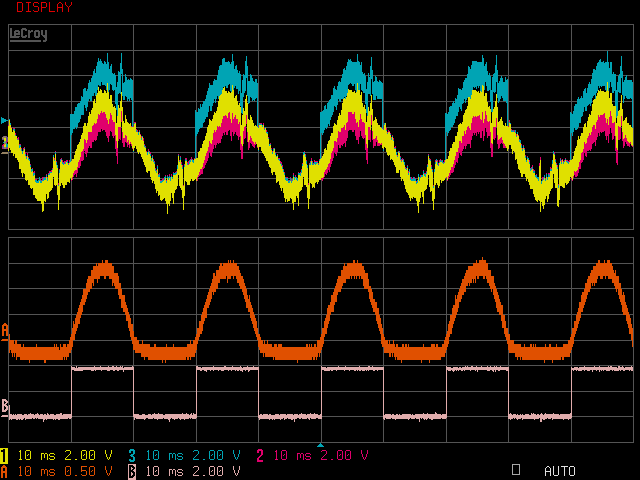

UART Master IP 1.0 の波形を示します。0x04 を受信した際の波形です。写真が見切れていると思うので、クリックして全体を表示してご覧ください。

UART Master IP は SRAM インターフェースでデータを読み書きします。O_RDATA が受信データ(Received Data)を出力する端子で、PC から FPGA にデータを送るとここに現れます。I_RADDR は読み込みたいレジスタのアドレスを指定します。0 が受信データを格納したレジスタ、5 がステータスレジスタになっています。

O_RDATA が I_RX_EN の立ち下がりエッジで変化しているのが分かります。I_RX_EN の立ち上がりのタイミングで I_RADDR が取り込まれ、I_RX_ENの立ち下がりのタイミングで指定したレジスタの内容が O_RDATA に出力されるという挙動になっています。

UART Master IP 1.0 は空読みしないと最新のデータを読めないバグと思われる挙動があり、そのために最初は 0x00 が読み出せていて、次に 0x04 が読めています。(O_RDATA が 0x61, 0x00, 0x60, 0x04 と変化している部分を言っています)

UART Master IP 1.1 の動作

UART Master IP 1.1 の波形を示します。先ほどと同様に 0x04 を受信した際の波形です。

O_RDATA の変化タイミングが I_RX_EN の立ち上がり時に変わりました。UART Master IP に接続された制御回路は変更していないので、正しく 0x04 が読めていないことが分かります。手元の検証では、I_RADDR を 0 にする期間をもう少し長くすると 0x04 が読めることが分かっています。

空読みバグが解消した代わりに、信号の動作タイミングが変更された、ということのようですね。Gowin IDE 1.9.8 以前で作成したプロジェクトを Gowin IDE 1.9.8.01 以降で開き、UART Master IP を再生成すると制御が上手くできなくなるので注意してください。

アドレスをI_RX_ENの立ち下がりで変化させたとき

I_RADDR の値を I_RX_EN の立ち下がりエッジで変化させつつ 2 クロック分保持させてみると、ver 1.0 の IP と同じように空読みが必要になる波形になりました。

アドレスをI_RX_ENの立ち上がりで変化させたとき

タイミングを少し変え、I_RADDR の値を I_RX_EN の立ち上がりエッジで変化させてみると、空読みが不要な波形になりました。

なんとなく、IP の使用方法としてはこちらが正統派な気がしますね。

回路を工夫して 1 つ前の I_RX_EN の立ち上がりでレジスタアドレスを変化させてみました。これでも空読みが不要な波形になりました。少々解せませんが……

RxRDYnは不安定

UART Master IP が出力する RxRDYn という信号を利用すれば、ステータスレジスタの最下位ビット(O_RDATA[0])が 1 になるのを検出する必要なく、さらにシンプルに受信できる気がします。UART Master IP ver 1.1 で検証してみます。

これは期待通り、受信データが読めています。

何度か実験すると、RxRDYn の変化がズレることがありました。タイミングがズレると空読みが必要な状況になってしまいます。結論としては RxRDYn の変化タイミングは信用できません。

UART Master IP 2.0 の動作

筆者がぱっと検証する限り、2.0 で大きく変更されたのは動作周波数を 50MHz から変更できるようになったことです。

1.1 までは 50MHz に固定でしたが、2.0 では好きな周波数に変更できるようになっています。

Tang Nano 4K に搭載された 27MHz の水晶発振器で UART Master IP を直接動かしてみましたが、ちゃんと動きました。

動作の方は 1.1 と同じ回路で同じように動き、特段の変化は見られませんでした。

投稿者の人気記事

-

uchan

さんが

2021/12/14

に

編集

をしました。

(メッセージ: 初版)

-

uchan

さんが

2021/12/15

に

編集

をしました。

(メッセージ: 詳しい実験結果を加筆)

-

uchan

さんが

2021/12/15

に

編集

をしました。

(メッセージ: 追加実験を実施)

-

uchan

さんが

2021/12/15

に

編集

をしました。

(メッセージ: RxRDYnを活用した読み込みを実験)

-

uchan

さんが

2021/12/15

に

編集

をしました。

(メッセージ: RxRDYnの変化は不規則)

-

uchan

さんが

2021/12/16

に

編集

をしました。

(メッセージ: リンク切れを修正)

-

uchan

さんが

2022/02/15

に

編集

をしました。

(メッセージ: バージョン2.0の検証を追記)

ログインしてコメントを投稿する