NE555(以下、555)の応用案として、オペアンプとLDOを組み合わせた、3.3V出力の降圧DC/DCコンバータを試作した。

以下のツイートのように、入力電圧VCCによらず出力電圧VOUTは3.3Vの一定出力を保つことができている。

本記事では、DC/DCコンバータの基本原理と、555のCTRL端子(5pin)を用いたDuty比の制御を説明した後、実際に試作したDC/DCコンバータの回路と、その測定結果について紹介していきたい。

まずは、今回作成した降圧型DC/DCコンバータの原理を説明する。

この章は、長いうえに数式による議論が多い。回路で必要な部分は後の章でも触れるので、理屈はいいから回路構成や実験結果を早く知りたい、という方は、この章を読み飛ばすことを推奨する。

試作回路を紹介する前に、今回作成した降圧DC/DCコンバータの動作原理を説明する。

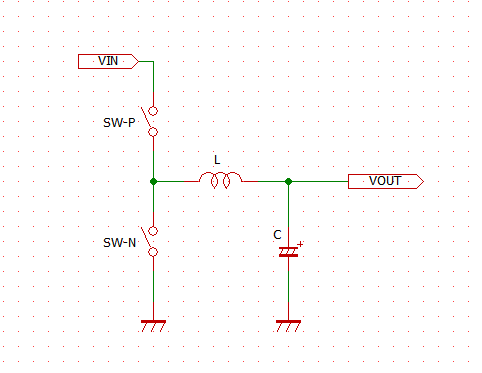

基本的な回路構成は、2個のスイッチとコイル、負荷コンデンサで構成される回路である。(下図)

この回路により、VINに対して、スイッチのON/OFF制御(スイッチング制御)を行うことで所望の出力電圧(VOUT)を得ることができる。

以下では、VINに対してVOUTをどのように決めることができるのか、その動作とともに説明したい。

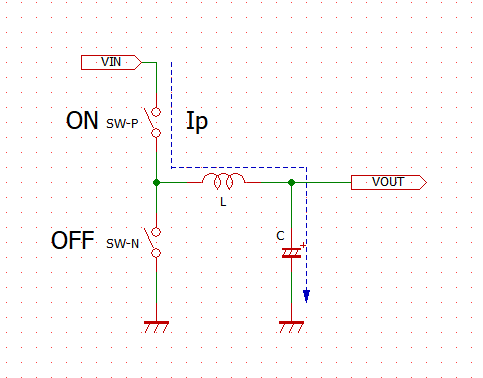

まず、上側のスイッチSW-PがONで、かつ、下側のスイッチSW-NがOFFのときのVOUT変化を考える。

このとき、VINからコイルを通じて、負荷コンデンサに電流が流入し、VOUTの電圧が上昇する。

この流入電流をIpとすると、IpとVIN電圧Vi、VOUT電圧Voの関係は以下のような微分方程式で表される。

Vi−Vo=LdtdIp(t)

ViとVoが、SW-PがONしている時間tpの間、ほぼ一定であるとすると、以下の関係が得られる。

Ip=LVi−Votp

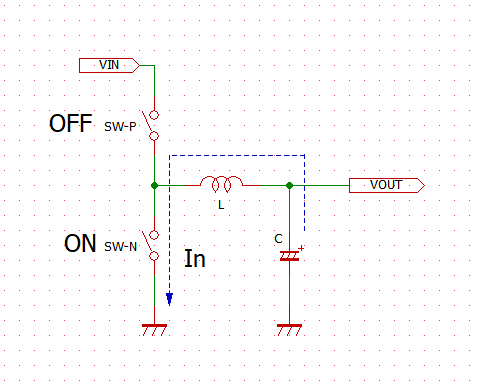

次に、上側のスイッチSW-PがOFFで、かつ、下側のスイッチSW-NがONのときのVOUT変化を考える。

このとき、負荷コンデンサに溜まった電荷は、コイルを通じてGNDに放電され、VOUTの電圧は低下する。

この放電電流をIpとすると、IpとVIN電圧Vi、VOUT電圧Voの関係は以下のような微分方程式で表される。

Vo=LdtdIn(t)

ViとVoが、SW-NがONしている時間tnの間、ほぼ一定であるとすると、以下の関係が得られる。

In=LVotn

VOUTが一定電圧を保持していると仮定すると、負荷コンデンサに流入する電流量と、放電する電流量は等しいはずである。すなわち、Ip=Inが成り立つ。先ほどの議論から、

Ip=LVi−Votp=LVotn=In

となり、これをVoについて解くことで、Voは、

Vo=tp+tntpVi=Duty×Vi

と表すことができる。なお、Dutyはスイッチング周期 tp+tn に対する、SW-Pのオン時間 tp の比である。

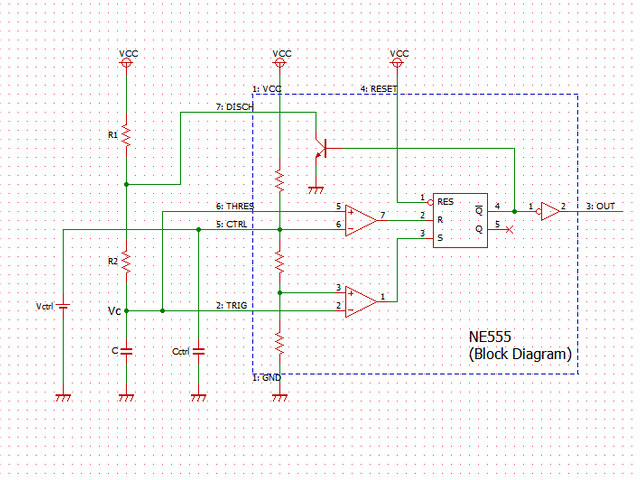

555をスイッチング制御に用いる前に、CTRLピン(5pin)に任意の電圧をかけた場合の無安定動作について検討する。

動作の概略については、taltalp氏の回路シミュレータで作るNE555タイマーが非常に分かりやすいので、まずは一読いただきたい。

本記事では、数式を用いて発振周期を詳細に求めていきたい。なお、以下の議論は下図の回路を想定して行い、回路定数も下図のものを用いる。

OUT端子がH/Lを維持しているとき、コンデンサCは充電/放電しており、Cの端子電圧Vcが変化している。

このVcをコンパレータで監視し、閾値電圧VthHを超えたときOUT端子はH→Lに、閾値電圧VthLを下回ったときL→Hに切り替わるようになっている。この閾値電圧は、CTRLの状態によって、以下のように求められる。

- CTRL端子に何もつながっていない場合 (通常動作):

VthH=32VCC,VthL=31VCC

- CTRL端子に任意の電圧αVCC (0<α≦1)がかかっている場合:

VthH=αVCC,VthL=21αVCC

OUT端子が切り替わってから再び切り替わるまでの時間、すなわち時間OUT端子がHまたはLを維持する時間は、Cに接続している抵抗R1, R2によって決まる。ここでは、 CTRL端子に任意の電圧αVCCがかかっている場合において、OUT端子がHの時間tHとLの時間tLを、それぞれ求める。

初期状態でOUT端子がHである場合を考える。この時、Vcの変化は、以下のように表せる。

Vc(t)=VCC[1−exp(−(R1+R2)Ct−t0n)]

ただし、t0nは、Vc(t0n)=0となる時刻とする。

OUT端子がL→H, H→Lに切り替わる時刻をそれぞれtrise, tfallとおくとき、

Vc(tfall)=VCC[1−exp(−(R1+R2)Ctfall−t0n)]

Vc(trise)=VCC[1−exp(−(R1+R2)Ctrise−t0n)]

と表せることから、

tfall=(R1+R2)ClnVCC−Vc(tfall)VCC

trise=(R1+R2)ClnVCC−Vc(trise)VCC

となる。したがって、OUT端子がHである時間tHは、

tH=tfall−trise=(R1+R2)ClnVCC−Vc(tfall)VCCVCCVCC−Vc(trise)

と書ける。ここで、条件よりVc(tfall)=VthH=αVCC、Vc(tfall)=VthH=αVCC/2となることから、

tH=(R1+R2)ClnVCC−αVCCVCCVCCVCC−αVCC/2

∴tH=(R1+R2)Cln(21⋅1−α2−α)

と表すことができる。

初期状態でOUT端子がLである場合を考える。OUT端子がHの時と同様、OUT端子がL→Hに切り替わる時刻をtrise、OUT端子がH→Lに切り替わる時刻をtfallとおくと、Vcの変化は以下のように表せる。

Vc(t)=Vc(tfall)exp(−R2Ct−tfall)

このとき、時刻triseにおけるCの電圧Vc(trise)は、

Vc(trise)=Vc(tfall)exp(−R2Ctrise−tfall)

と表せることから、OUT端子がLである時間tLは、

exp(−R2Ctrise−tfall)=Vc(tfall)Vc(trise)

∴tL=trise−tfall=R2ClnVc(trise)Vc(tfall)

と書ける。OUT端子がHの時と同様、Vc(tfall)=VthH=αVCC、Vc(tfall)=VthH=αVCC/2であるので、

tL=trise−tfall=R2ClnVCC/2VCC=R2Cln2

と表される。

以上をまとめると、CTRL端子に電圧αVCCをかけたとき、OUT端子がH/Lを維持する時間は

tH=(R1+R2)Cln(21⋅1−α2−α)

tL=R2Cln2

となり、CTRL端子の電圧を上げるとtHが長くなり、OUT端子がHになる時間のみが長くなる。

また、発振周期$Tは、

T=tH+tL=(R1+R2)Cln(21⋅1−α2−α)+R2Cln2

と表され、周期Tに対するL時間のDuty比DLは、

DL=TtL=(R1+R2)Cln(21⋅1−α2−α)+R2Cln2R2Cln2

と表すことができる。

ここまで長々と議論してきたが、555で降圧DC/DCコンバータを作るうえで重要なのは、以下の2点である。

- 降圧型DC/DCコンバータの出力電圧Voは、入力電圧Viとスイッチング制御のDuty比で以下のように表される。

Vo=tp+tntpVi=Duty×Vi

- 555のCTRL端子に任意の電圧αVCCを入力すると、周期Tに対するL時間のDuty比DLは以下のように表される。

DL=TtL=(R1+R2)Cln(21⋅1−α2−α)+R2Cln2R2Cln2

これらを用いることで、555を用いた降圧型DC/DCコンバータを組むことができる。

以下では、作成した回路とその測定結果を紹介していく。

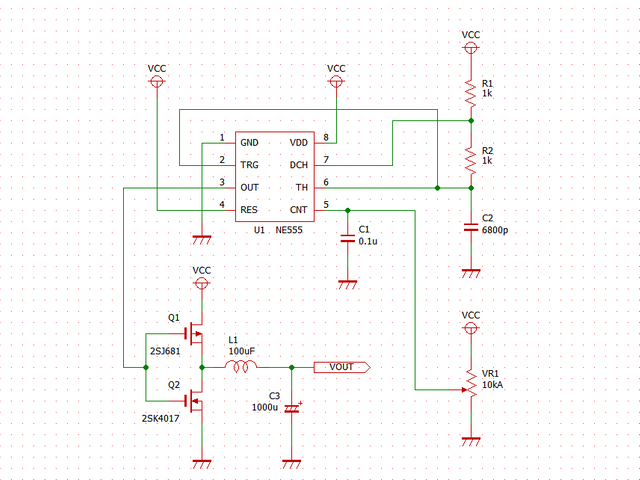

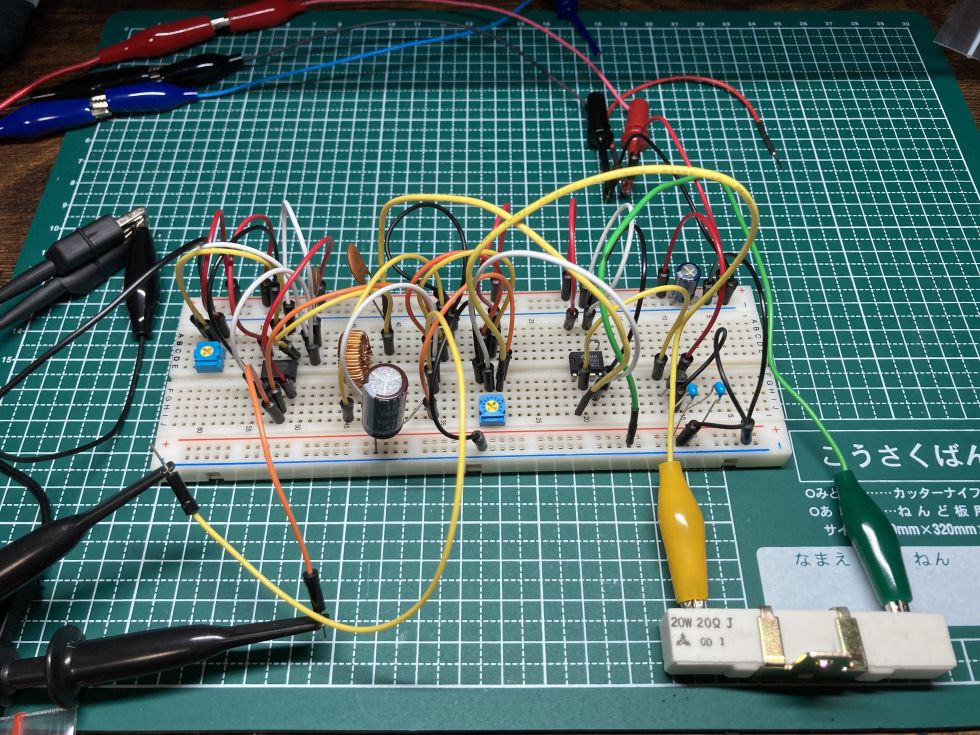

まずは、CTRL端子に任意の電圧をかけられるよう、ボリュームを用いた回路で実験を行った。

555による発振回路、555のCTRLの電圧調整用のボリューム、電圧出力のためのSW (MOSFET)、コイル、負荷コンデンサで構成している。(下図)

上記の回路により、可変抵抗でCTRL端子にかかる電圧を変えることで、下記ツイートのようにDC/DCの出力電圧Voutを変えることができた。

なおツイートの画像は、1枚目は測定環境を、2~4枚目がCTRL電圧を変えたときのVOUTの変化を示しており、2~4枚目の波形は、水色がDC/DCコンバータの出力Voutの、黄色が555のOUT端子電圧の時間変化を表している。

この構成により、CTRL端子の電圧を変えることにより、発振のDuty比を変えることができ、出力電圧をVoutを変えることができた。

しかしこの回路は、2つの改善点が存在する。

- ボリュームの位置を固定している状態でVCCが変化したとき、出力電圧Voutも連動して変化する。

すなわち、ラインレギュレーションが悪い。

- 出力Voutに抵抗値の低い負荷を接続すると、負荷に流れる電流によって出力電圧も連動して変化する。

すなわち、ロードレギュレーションが悪い。

これらは、DC/DCコンバータの主な用途である安定化電源として用いる場合には、とても都合が悪い。

なぜなら、安定化電源の用途はそもそも、入力電圧の変動や出力電流の変動に対して、出力が変動してほしくない機器の電源だからである。

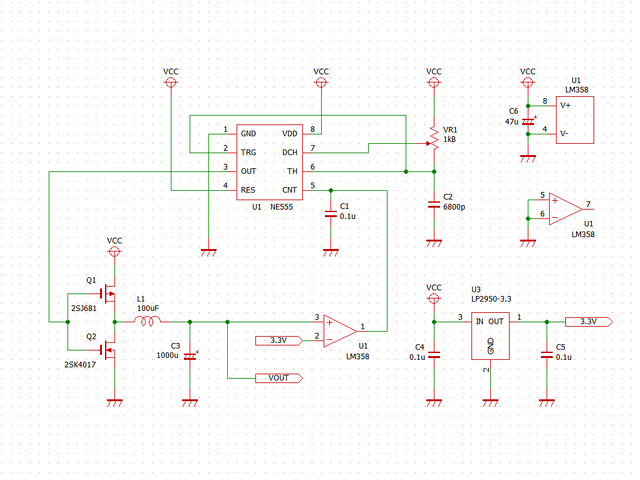

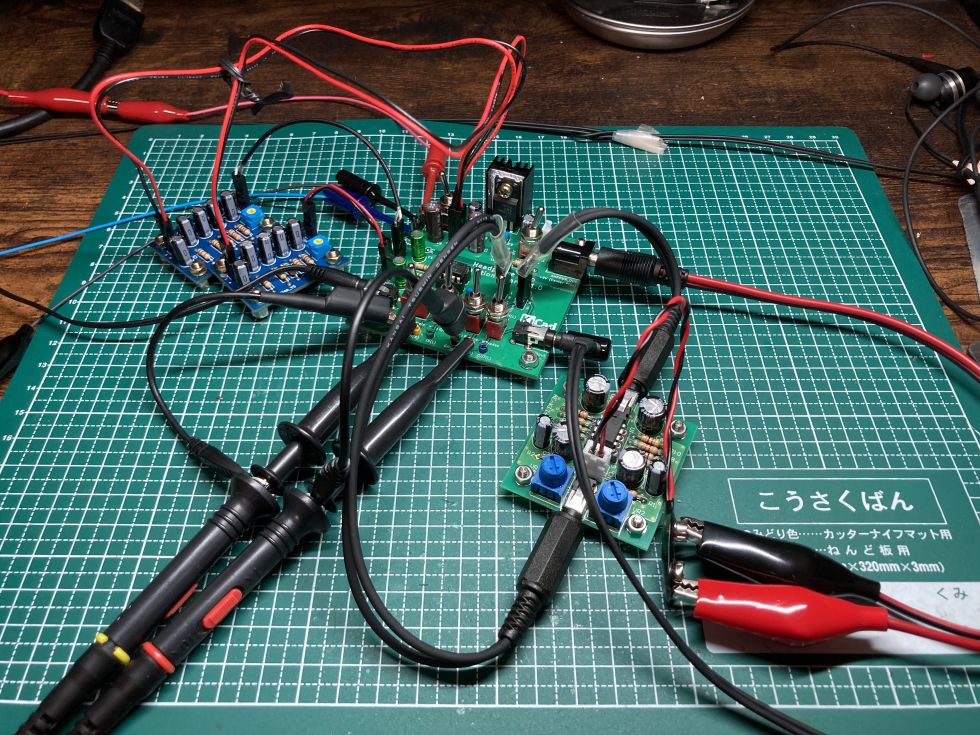

上記の改善点を解決する方法の一つとして、出力電圧Voutの変化を読み取り、それに応じてスイッチング制御のDuty比を変える、フィードバック制御が挙げられる。このフィードバックを実現するために、オペアンプと、LDOによる基準電圧を追加した。(下図)

この回路追加により、Voutが上昇した場合は、その上昇量に応じてCTRLの電圧を上げることで、Duty比DLを下げ、上がったVoutを下げようとし、Voutが低下した場合は上昇時と逆に下がったVoutを上げようとすることで、Voutを一定に保つことができる。このフィードバックループを作ることにより、この時VoutはオペアンプのV+とV-の電圧が一致させるように制御が働き(イマジナリーショート)、3.3Vに保たれる。

実際、この構成でDC/DCの出力Vout(水色)と555のOUT端子の電圧(黄色)の出力を確認すると、Voutの変化に対してOUT端子の発振周波数が変化していることがわかる。

なお、CTRL端子の電圧が変わるとDuty比が変わると説明したが、実際にはOUT端子がHになっている時間tHだけである(DC/DCの動作としてはSW-Nのオン時間のみが伸びる)。

このため、この制御は、Duty比だけでなく動作周波数1/Tも変化する、PFM(Pulse Frequency Modulation)制御である。

上記の改善点で上げた、入力電圧と出力負荷の変化に対するVoutの安定性を確認結果を以下に示す。

入力電圧VCCを5V, 7.5V, 10V, 12Vに変えたときの出力電圧Voutの変化を以下に示す(いずれの条件においても、負荷抵抗なし)。いずれの波形も、入力電圧VCCを水色、出力電圧VOUTを黄色で示している。入力電圧が上がると、出力電圧の揺れが大きくなるものの、おおよそ3.3Vを保持できていることがわかる。

出力負荷を無負荷, 1kΩ, 220Ω, 20Ωに変えたときの出力電圧Voutの変化を以下に示す(いずれの条件においても、VCC=5V)。いずれの波形も、入力電圧VCCを水色、出力電圧VOUTを黄色で示している。入力電圧の変化と異なり、出力負荷の抵抗値が変わってもVoutの揺れはほとんど変わらないことがわかる。

以上のように、555とオペアンプを組み合わせることで、入力・出力の状態によらず一定出力を保つ、降圧DC/DCコンバータの実現に成功した。

最後に、今回の達成事項のまとめと、今後の課題を示す。

達成できたこと

入力電圧や負荷によらず、一定の出力電圧を保つことのできる、降圧DC/DCコンバータを設計・試作できた。

今後の課題

・出力電圧を自在に変更すること。(今回は電圧源の電圧3.3Vしか出力できない)

・PFM制御を効果的に行うには、可変抵抗VR1を適切に調整する必要があること。(調整なしで発振周波数を決めたい)

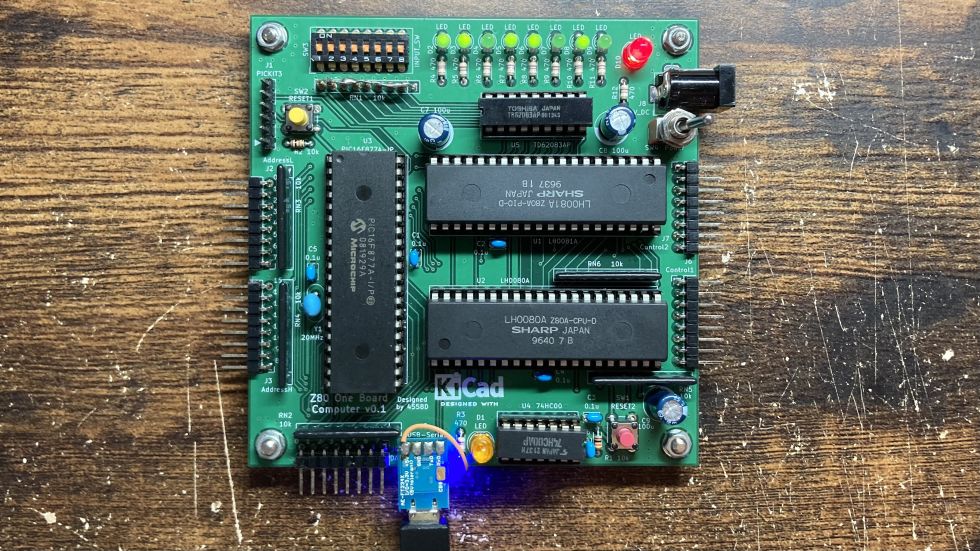

製作品

製作品  4041

4041

-

4558D

さんが

2022/03/27

に

編集

をしました。

(メッセージ: 初版)

-

4558D

さんが

2022/03/27

に

編集

をしました。

-

4558D

さんが

2022/05/30

に

編集

をしました。

ログインしてコメントを投稿する