前回の記事 GowinのOSER10検証 その1 の続きです。OSER10 の出力の位相が PCLK とずれる原因が判明し、解決できました。

原因

結論から言えば、OSER10 の出力と PCLK がズレるのは OSER10 の仕様のようです。ズレないためには、PCLK も OSER10 を通す必要があります。

元の回路構成

これまで、次の回路構成で実験をしていました。

OSER10 の入力に供給している PCLK をそのまま FPGA の端子に出し、それを観測していました。

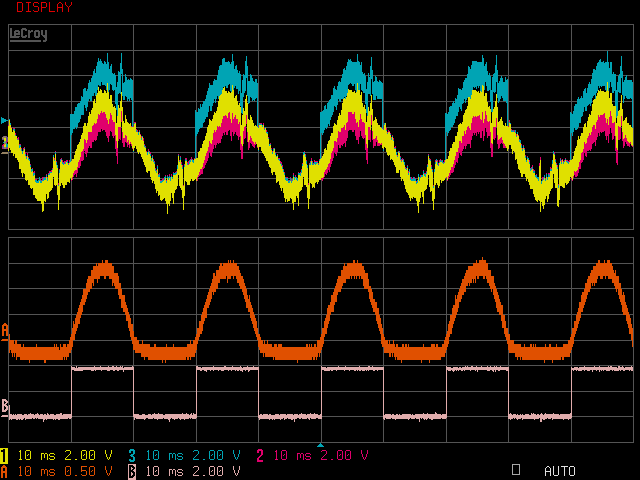

修正した回路構成

次のような回路構成に変更したところ、位相のズレが解決しました。

PCLK は FCLK/5 の周波数です。つまり、OSER10 を使って 1111100000 というビット列を出せば PCLK と同じ周期の信号になります。

投稿者の人気記事

-

uchan

さんが

2026/01/15

に

編集

をしました。

(メッセージ: 初版)

ログインしてコメントを投稿する