製作品

製作品  3819

3819NE555で可変電圧出力の降圧DC/DCコンバータを作ってみた

はじめに

先日、NE555で3.3V出力の降圧DC/DCコンバータを作ってみたという記事を投稿した。記事末尾に、今後の課題として「出力電圧を自在に可変すること」と「調整なしで発振周波数を決めること」の2点を記載した。

これらの課題に対してNE555 (以下、555)の単安定モードを用いた、PFM方式の降圧DC/DCコンバータを考案し、出力電圧を簡単に変えることができることを確認できた。本記事では、その回路構成と動作原理を簡単に説明した後、その測定結果について説明したい。

試作回路の説明

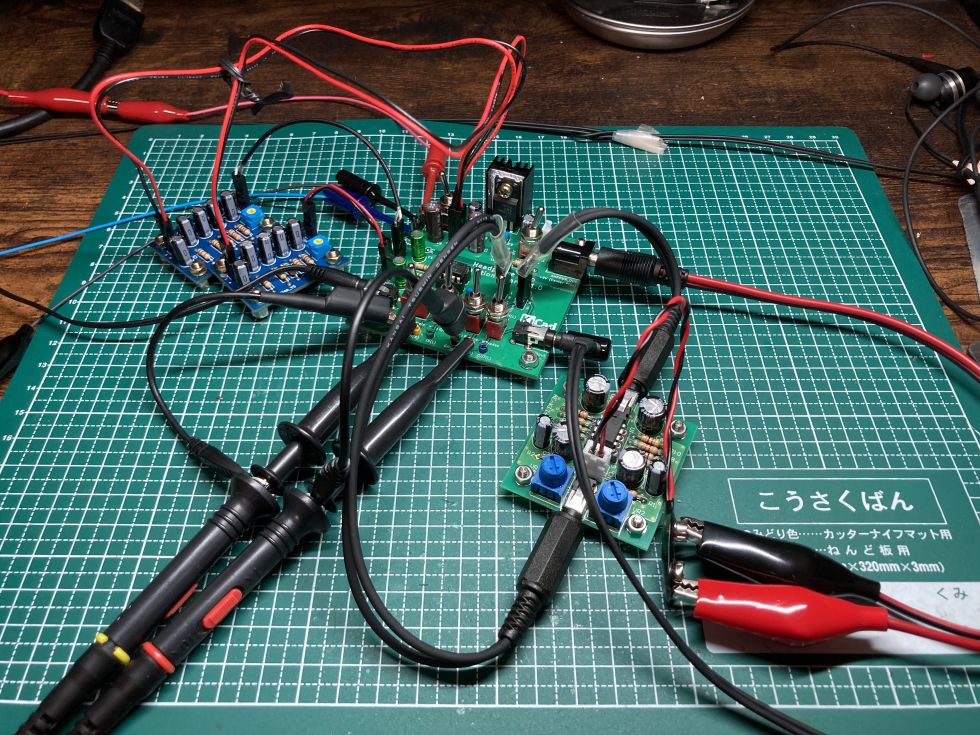

今回試作した回路を下図に示す。

前回の回路からの変更点は、以下のとおりである。

- フィードバック出力を、CNT(5 pin)からTRG(2 pin) に変更したこと。

- オペアンプ(LM358)をコンパレータ(LM2903)に変更したこと。

- フィードバックの入力に抵抗分圧を入れたこと。

1,2については、前回回路では、オペアンプのアナログ出力を555のCNTピンに入れていたことで、出力電圧に応じて発振周波数を連続的に変え、出力電圧を調整していた。これに対し、今回の回路では、オペアンプの代わりにコンパレータを用い、3.3Vの基準電圧(以下、VREF)との単純な比較により、TRG(2 pin)信号を生成している。

3の変更をしない場合で説明すると、この制御により、VOUT > VREFの時になるとローサイドFET(Q2)を一定時間ONして電圧を下げ、一定時間経った後にハイサイドサイドFET(Q1)をONし、VOUT > VREFになるまでVOUT電圧を上げ続け、平均しておよそVOUT = VREFを維持することができる。

3については、VOUTを抵抗分圧により低くした電圧をVREFに合わせようとする。これによって、分圧前のVOUT電圧は、分圧後の電圧を分圧比で割った電圧で安定する。

つまり、可変抵抗VR1の1-2端子間の抵抗 (GND側)を、2-3端子間の抵抗 (VOUT側)をとしたとき、分圧比は

となり、VOUTの電圧は、

と表すことができる。

今回の回路構成において出力電圧は、この分圧比とVREFの電圧によってのみ決まるため、簡単な回路構成で電圧可変のDC/DCコンバータを作ることができる。

Q1, Q2のON時間とDuty比

回路構成の説明では簡単に流したが、ここで軽くハイサイド/ローサイドFET(Q1/Q2)のON時間、と、そのDuty比を求めておきたい。ここでは簡単のため、として考える。

まず、Q2のON時間は、555によるワンショットタイマーのON時間なので、回路図から以下のように求められる。

次に、Q1のON時間をを求める。は、Q2が時間だけONすることで下がったVOUT電圧が、VREFまで戻るまでにかかる時間を表している。まず、Q2がONになった瞬間のVOUT電圧を求める。

Q2がオンの時、負荷容量C3に溜まった電荷が、Q2を介して放電することによって電圧降下するので、

と表される。ただし、はQ2のON抵抗を表す。

時刻でQ1がオンになると、VOUT電圧がVREFまで戻るので、戻るまでの時間は

となる (はQ1のON抵抗)。ここで、先ほど求めたを代入すると、

となり、が求められた。

以上から、この回路構成におけるDuty比は、

と表される。

前回の回路構成では、Duty比はあくまで555の発振周波数を決めるための抵抗・コンデンサによってのみ決まっていたが、今回の回路構成ではDuty比は出力容量C3やQ1、Q2のON抵抗にも影響を受けることがわかる。

実験結果

以下では、今回の回路構成における、可変抵抗VR1を変えたときの出力電圧のオシロ波形と、前回回路で測定したラインレギュレーションとロードレギュレーションの波形、そして出力容量C3を変えたときの波形を示す。

出力電圧

今回の回路構成では、可変抵抗VR1を調整することで、出力電圧を変えることができる。下表は、入力電圧を12Vに固定し、可変抵抗VR1の角度を変えたときの、可変抵抗の位置と出力波形を表している。なお、出力波形は、水色はVOUTを、黄色は555のOUT端子電圧をそれぞれ表している。

可変抵抗を時計回りに回し切った時、分圧比は1になっているので、出力電圧はVREF電圧、すなわち3.3Vを出力する。この状態から可変抵抗を反時計回りに回していくことで、設定電圧を高くすることができる。ただし、設定電圧が10V前後になると出力電圧が安定しなくなる。さらに、VR1を反時計回りに回し切ると発振は止まり、出力電圧は入力電圧に張り付く。

ラインレギュレーション (出力電圧3.3V)

入力電圧VCCを5V, 7.5V, 10V, 12Vに変えたときの出力電圧VOUTの変化を以下に示す(いずれの条件においても、負荷抵抗なし)。いずれの波形も、出力電圧VOUTのDC波形を水色、AC波形を黄色で示している。前回回路では、入力電圧が高くなると出力電圧の変動が著しく大きくなっていたが、今回の回路ではその変動幅がかなり小さく抑えられており、入力電圧の変化に対して出力がより安定していることがわかる。

ロードレギュレーション (出力電圧3.3V)

出力負荷を無負荷, 1kΩ, 220Ω, 20Ωに変えたときの出力電圧VOUTの変化を以下に示す(いずれの条件においても、VCC=5V)。いずれの波形も、出力電圧VOUTのDC波形を水色、AC波形を黄色で示している。前回回路と同様、出力負荷の抵抗値が変わってもVOUTの揺れはほとんど変わらないことがわかる。

出力容量(C3)の大きさ

DC/DCコンバータの出力VOUTにつながるコンデンサC3の容量は、これまでの測定では1000uFを用いたが、これを小さくしたとき、VOUT波形はどのように変わるだろうか。下表は、入力電圧を7.5V、出力電圧を3.3Vに固定し、C3を0.1uF (積セラ)、1uF, 10uF, 47uF, 100uF, 1000uFに変えたときの出力波形を示しており、水色はVOUTを、黄色は555のOUT端子電圧をそれぞれ表している。

C3が小さい条件(C3 = 0.1uF, 1uF)では、出力波形が正弦波の合成波になっており、スイッチング制御で意図した出力波形となっていない。これは、VOUTからコンパレータを介して555にされているフィードバックループの位相余裕が足りず、出力が発振しているからであると考えられる。

また、C3≧10uFでは意図した出力波形となっているが、C3が大きくなればなるほど電圧変動が小さく、より安定した出力が出せるようになることが確認できる。

まとめ

以上のように、555とコンパレータを組み合わせることで、前回の課題であった、出力電圧の可変とPFM制御の周波数設定を容易に行うことができるようになった。最後に、今回の達成事項のまとめと、今後の課題を示す。

達成できたこと

・入力電圧や負荷の状態によらず、設定した電圧を出力できるようになった。

・1個の可変抵抗の調整だけで、出力電圧の設定値を変えることができるようになった。

・PFM制御の周波数設定を煩雑な調整なしでできるようになった。(設定が不要になった)

・前回回路と比較し、ラインレギュレーションが改善した。

今後の課題

VOUTにつけるコンデンサの容量が小さいと出力が発振する。(1uF以下で出力の位相発振が見られる)

投稿者の人気記事

-

4558D

さんが

2022/04/03

に

編集

をしました。

(メッセージ: 初版)

-

4558D

さんが

2022/04/03

に

編集

をしました。

-

4558D

さんが

2022/05/30

に

編集

をしました。

ログインしてコメントを投稿する