4558D が 2022年07月08日14時56分29秒 に編集

コメント無し

本文の変更

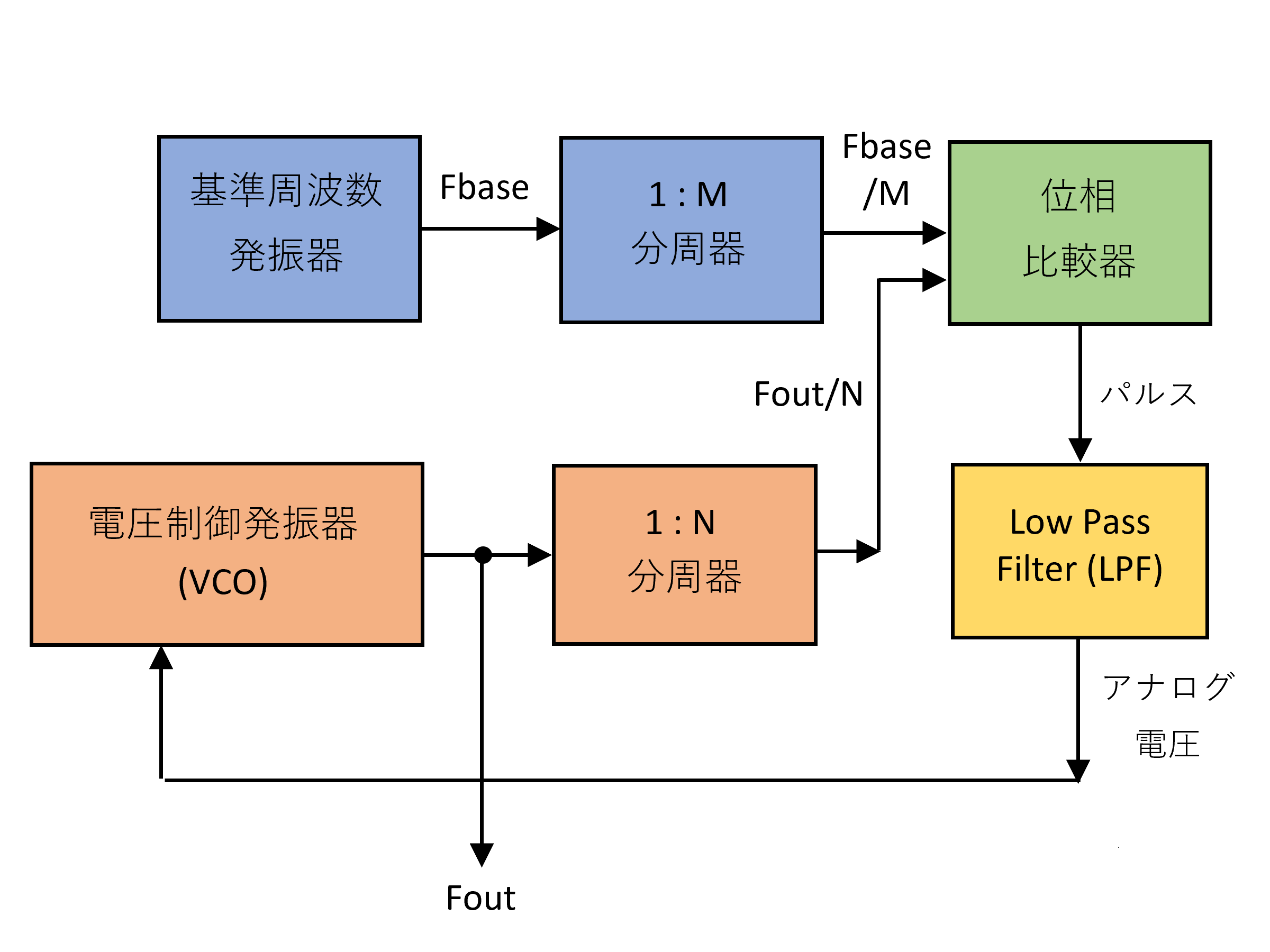

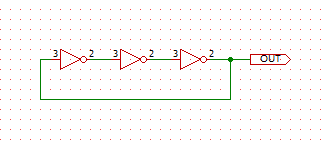

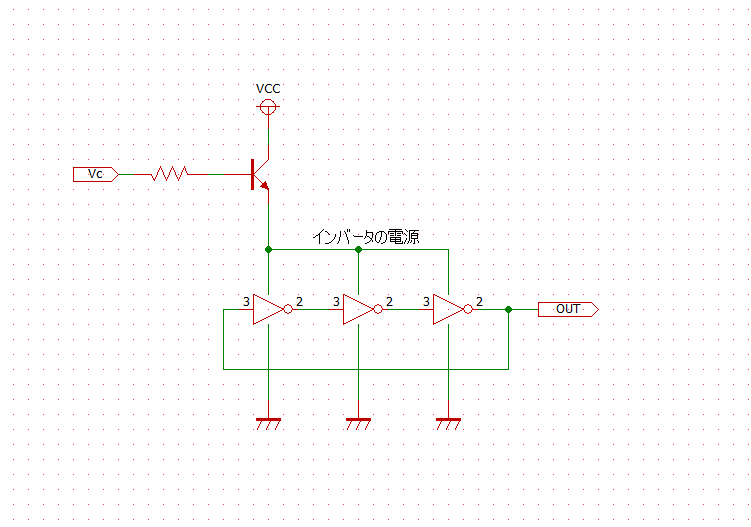

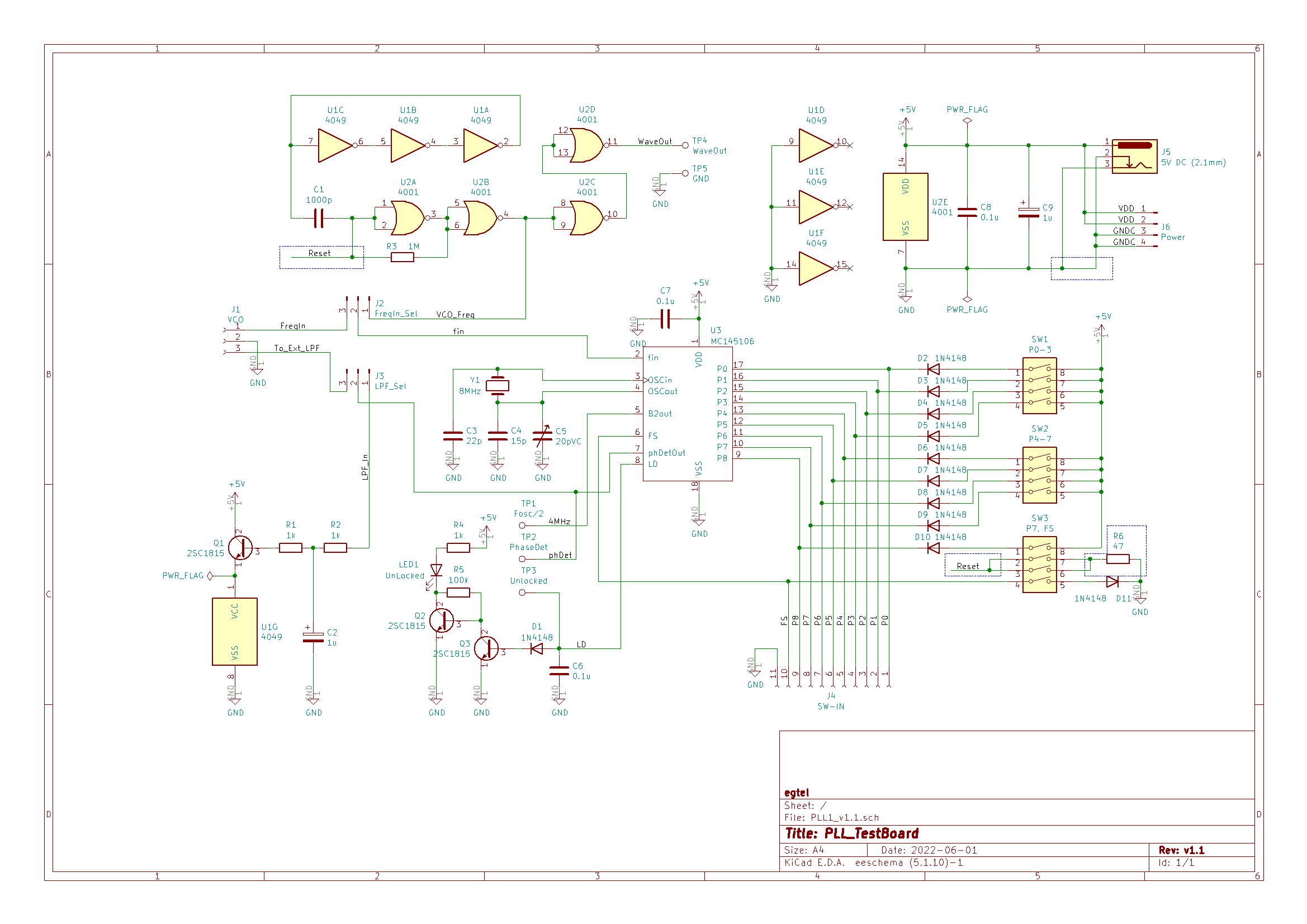

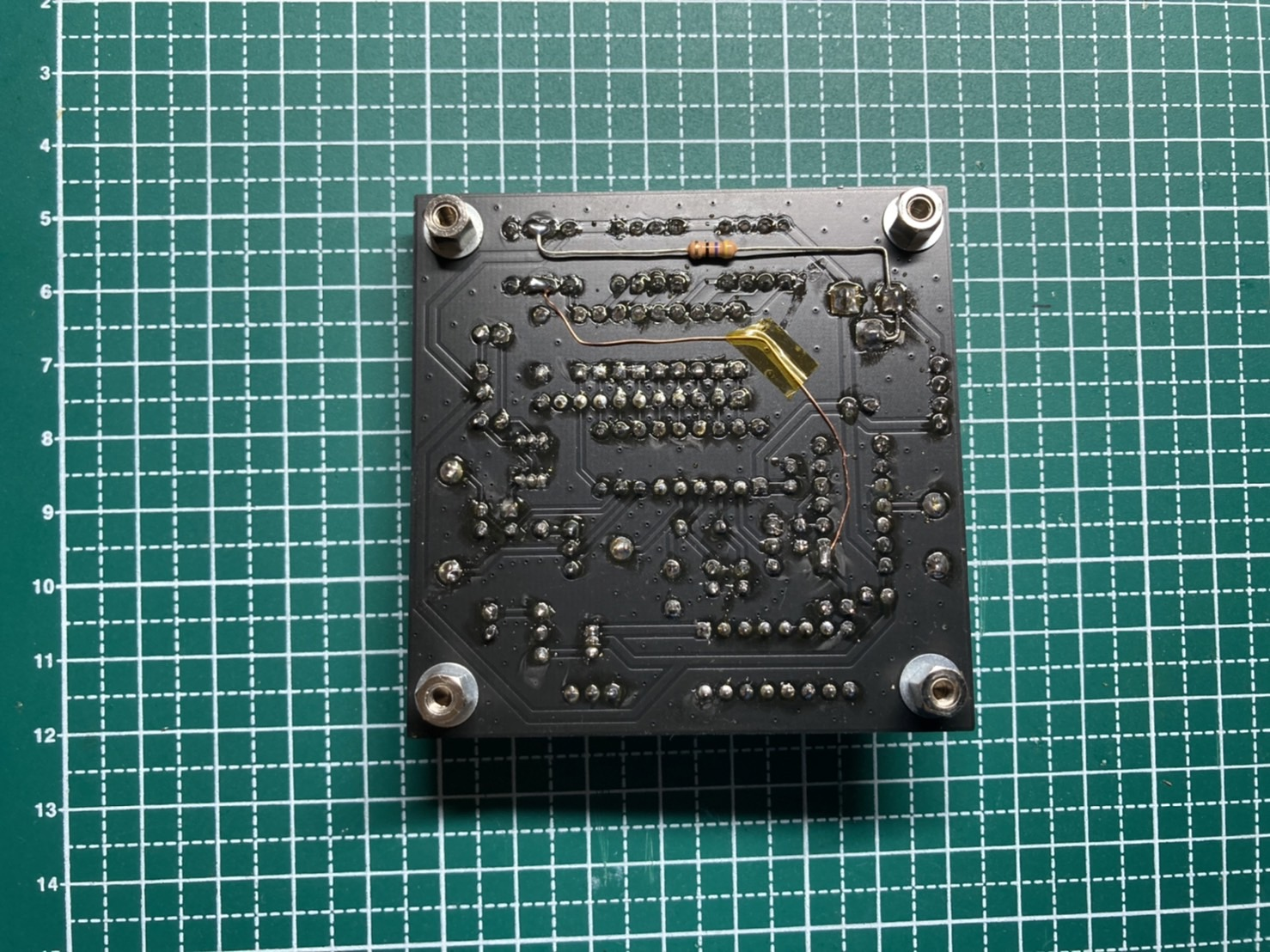

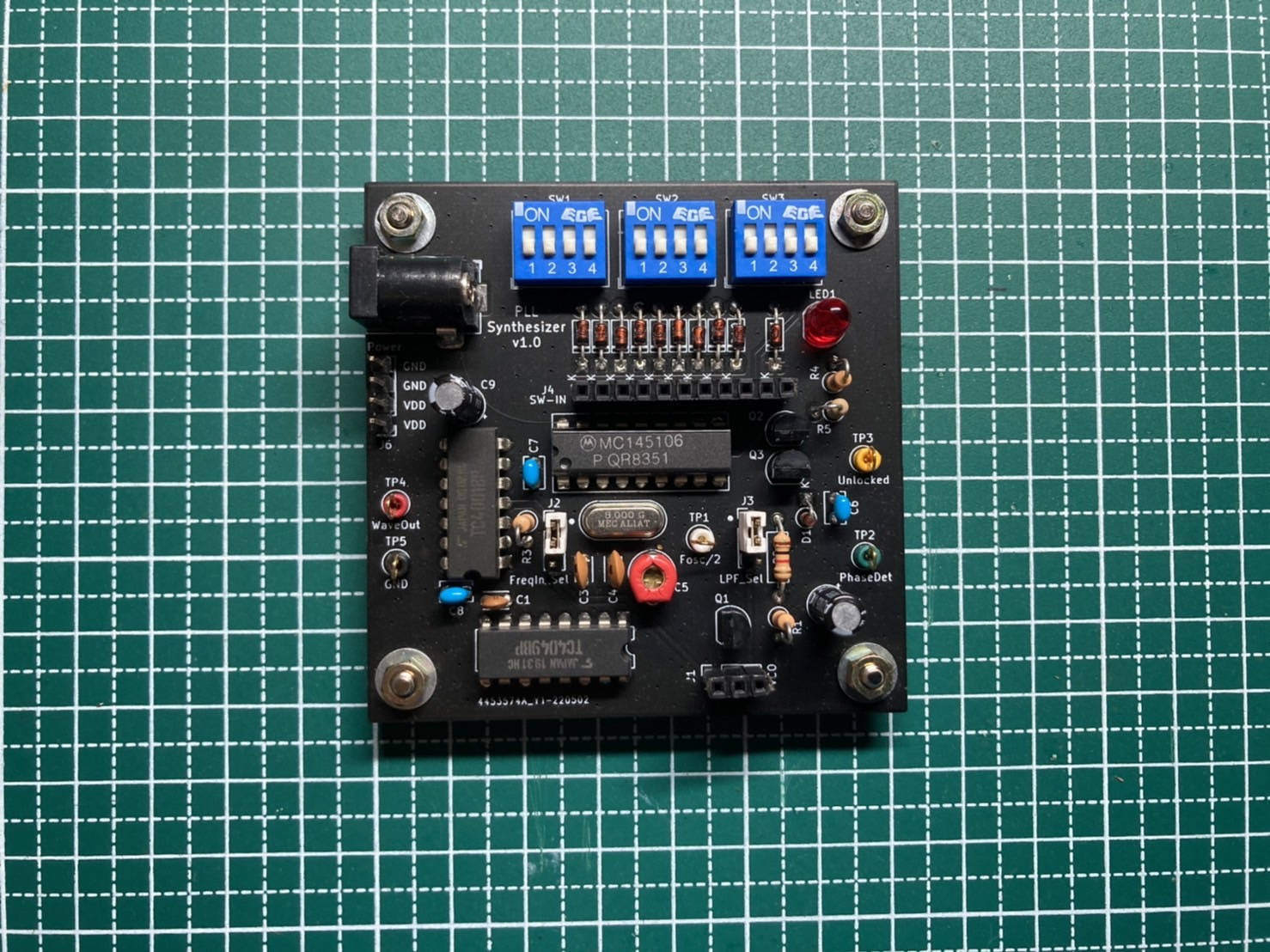

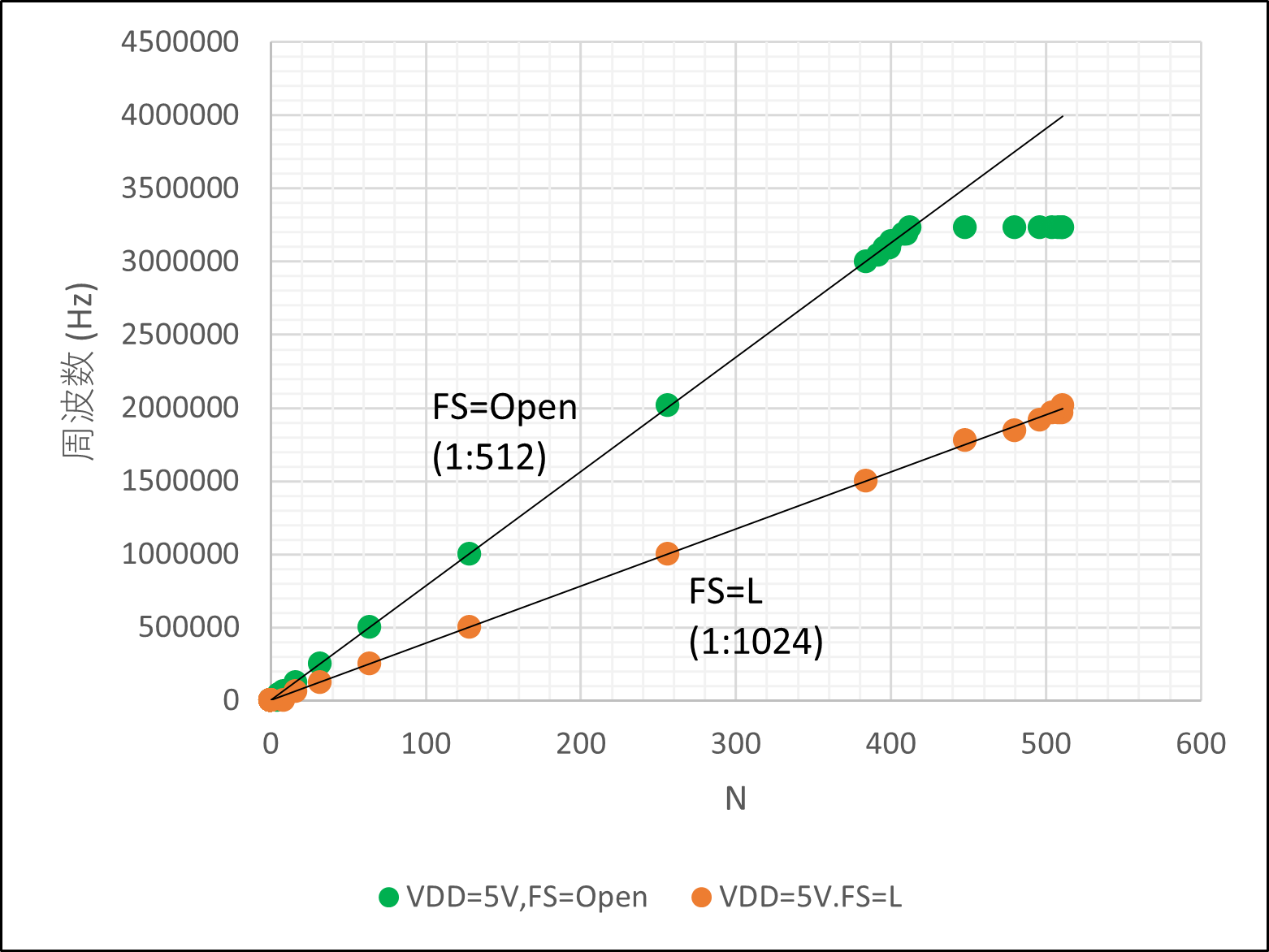

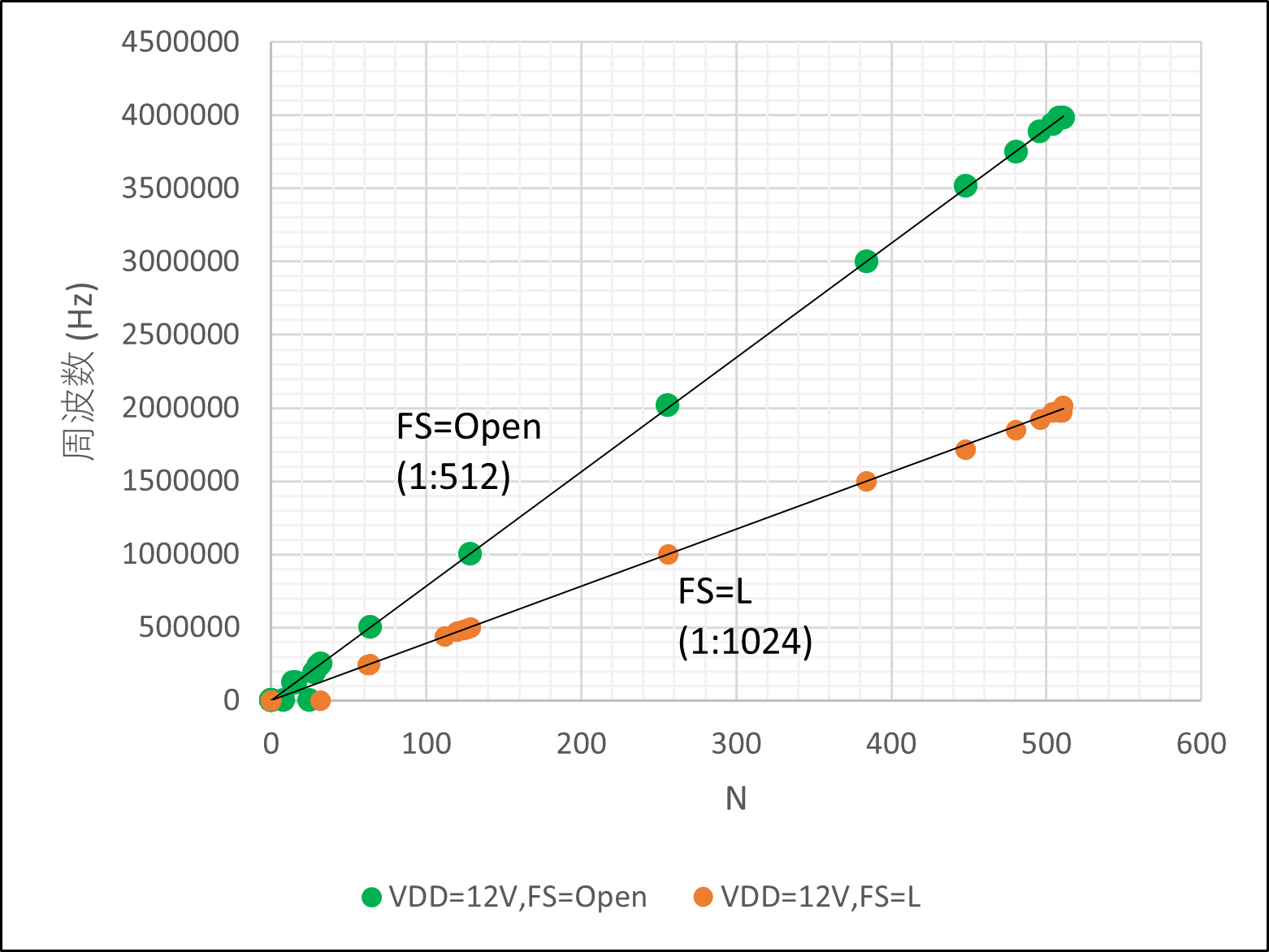

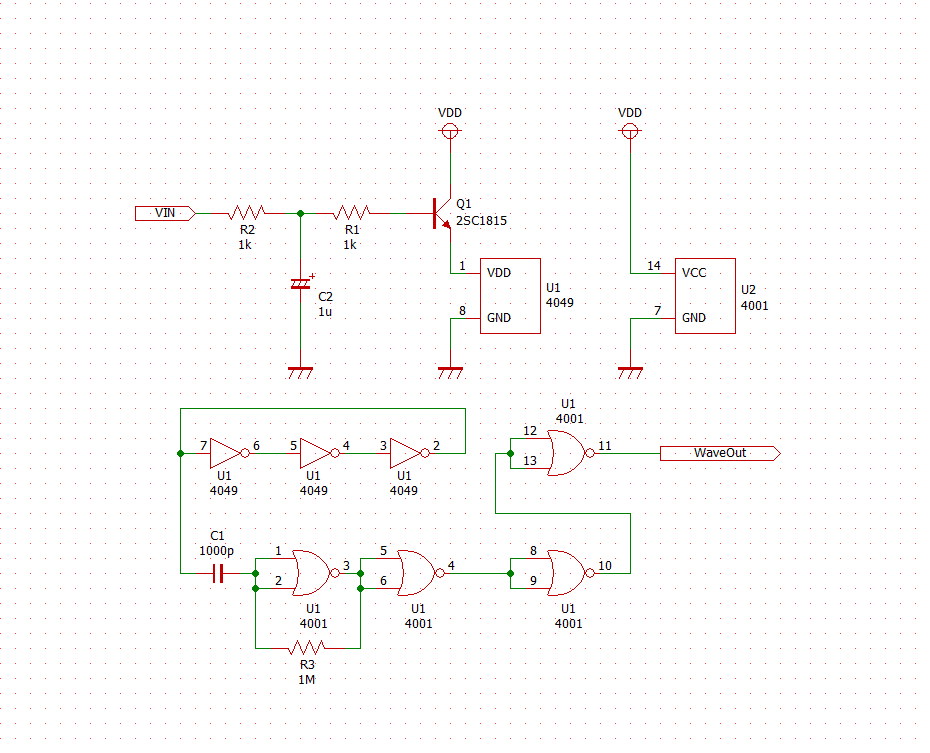

# はじめに 大阪日本橋のデジットで、PLLシンセサイザICのMC145106が21個300円 (2022年5月現在)で売られており、興味本位で購入してみた。 ネット上に資料が少なく、PLLとして動作させるまでにかなり苦労したが、最終的な成果として最大4MHzの矩形波を出すことのできるPLLシンセサイザを作成し、スイッチの切り替えによって発振周波数を切り替えることに成功した。 本記事では、その回路構成、作成した基板、そして、性能の測定結果を紹介していきたい。 @[twitter](https://twitter.com/electrotelecast/status/1525728850747195394?s=20&t=9BtqyMSHrOPJVYaIpQMTMA) # 回路説明 ## 全体の回路構成 まず、制作したPLLシンセサイザのブロック構成を示す。基準周波数と電圧制御発振器(VCO)の出力周波数を位相比較器で比較し、比較結果からVCOの入力電圧を変えて出力周波数を再設定する、という制御を行うことで、出力周波数を一定にすることができる。この構成を、MC145106とリング発振器を用いて実現した。これらについて、次セクションで説明する。  ## MC145106 MC145106は、モトローラ社が製造する、CMOS構成のPLLシンセサイザ―である。データシートによると、CB無線機やFMトランシーバーに利用できるようである。基準発振器、周波数入力、分周器、位相比較器がワンチップに収まっている。このため、VCOとLPFを用意すれば、少ない外付け部品数でPLLシンセサイザを制作することができる。詳細なブロック図は[こちらのサイト](http://uni9999.cocolog-nifty.com/blog/2014/08/mc145106.html)が詳しい。 ### 発振周波数の設定 基準発振器の出力周波数$F_{base}$に対する分周比$M$は、FS端子(6 pin)で設定できる。FS=Hにすると$M=2 \times 512$に、FS=Lにすると$M=2 \times 1024$に設定できる。また、VCOの出力周波数$F_{out}$に対する分周比は、P0~P8端子(17, 16, ..., 9 pin)設定できる。これらのピンをLレベル、もしくは、解放にしたときを0、Hレベルにしたときを1としたとき、分周比$N$は、下表のように2進数的に決めることができる。 | P0 - 8 | $N$ | |:---:|:---:| | 0 0000 0000 | 2※ | | 0 0000 0001 | 3※ | | 0 0000 0010 | 2 | | 0 0000 0011 | 3 | | 0 0000 0100 | 4 | | $\cdots$ | $\cdots$ | | 0 1111 1111 | 255 | | $\cdots$ | $\cdots$ | | 1 1111 1111 | 511 | ※ P0-8 = 000000000, 000000001の場合は$N=2,3$にセットされる。 以上のようにして決めた分周比により、出力周波数$F_{out}$は以下のように決めることができる。 $$ F_{out} = \begin{cases} \frac{N}{512\times 2} F_{base} & \text{if} & FS=H & or & Open \\ \\ \frac{N}{1024\times 2} F_{base} & \text{if} & FS=L \end{cases} $$ また、外付け部品の接続方法に関して、データシートには詳細な説明はないが、[こちらのサイト](https://www.radioexperimenter.us/rm-1995-11/info-myh.html)に情報が載っていたため、本記事の回路設計の参考にさせていただいた。 ## 電圧制御発振器(VCO) 本記事のPLLシンセサイザでは、CMOSインバータによるリング発振器を応用することでVCOを実現した。 リング発振器は、CMOSインバータを奇数個組み合わせることで作られる発振器である。例えば、インバータを3個直列で接続した場合の回路構成は下図のようになる。  この発振器の発振周波数は、おおよそ、個々のインバータの応答速度とその段数で決まる。(と言うより、それ以外に影響してくる要素がない) そのため、発振周波数を調整するには、インバータの段数、もしくは応答速度を変化させればよい、ということになる。CMOSのインバータの応答速度は、インバータが流す消費電流が多くなると早くなる、という性質があるため、インバータに流す電流が少なければ発振周波数を低く、消費電流が多ければ発振周波数を高くすることができる。 そのため、リング発振器で電圧制御発振器 (VCO)を作る場合は、下図のようにトランジスタのベース電圧を変えることで制御することでインバータの消費電流を変え、発振周波数を変える、という方法をとるとよい。本記事のように、PLLシンセサイザのVCOとして用いる場合は、位相比較器の出力をローパスフィルタで平滑化してVcに入れ、OUT出力の信号を、PLLの周波数入力に入れることで実現できる。  最終的な回路構成、および、使用部品の決定の際は、[こちらのサイト](http://lonvic.web.fc2.com/WorkShop/49_VCO/CIR-4049UB.html)を参考にさせていただいた。 ## 全体の回路図と作成した基板 最後に、制作した基板全体の回路図を下図に示す。 回路図中の青破線で囲んだ部分は、基板を発注後に追加した部分であり、VCOのリセットスイッチの追加と、DCジャック周りの配線を少し修正している。 以上の回路を70mm×70mmサイズに収めた。回路図の青枠線部分で示した追加配線と抵抗は基板裏側に直接取り付けている。   # 性能測定 作成した基板に対して、PLLシンセサイザ―として設定できる周波数と、VCO単体の入力電圧に対する出力特性を測定した。以下では、その測定結果を簡単に示す。 ## PLLシンセサイザの性能 ### スイッチと周波数の関係 P0~P8の入力を切り替えて$N$を設定することで、出力周波数を測定した。測定時の電源電圧は、VDD=5V, 12Vの2つを設定し、それぞれにおいてFS=Open, Lをそれぞれ設定した。この条件での測定結果を以下に示す。緑およびオレンジの点は実測結果を、黒の実線は、先述の計算式から得られる出力周波数の理論値をそれぞれ表している。また、周波数が0Hzになっているのは、スイッチにより$N$を設定して測定したものの、そもそも発振できていなかったり、発振周波数が不安定であること示している。   どちらの電圧でも、FSをOpenからLに切り替えることで、周波数を半分に、LからOpenで周波数を2倍に、それぞれ切り替えることができている。VDD=5Vでは、FS=Openにしたとき出力周波数の上限は約3.2MHzで頭打ちになっているが、VDD=12Vでは約4MHzまで、理論値どおりの出力ができている。一方で、VDD=12VよりもVDD=5Vのほうが、$N$が小さいときも理論値どおりの周波数で発振できることがわかる。 ### 発振波形 VDD=12V, FS=Openの条件下で、Nを変えたときの発振波形を以下に示す。以下に示した範囲では、ほぼ理論値通りに設定した周波数を出力できることがわかる。  ## VCOの性能 ### 入力電圧と発振周波数の関係 今回作成したPLL基板は、ジャンパLPF_Sel (J3)の1,3ピン間を短絡することで、VCOの測定回路を作ることができる。 この測定回路の入力電圧VINを0Vから上げていき、出力端子WaveOutの出力周波数を測定することで、VCOの性能を測定できる。

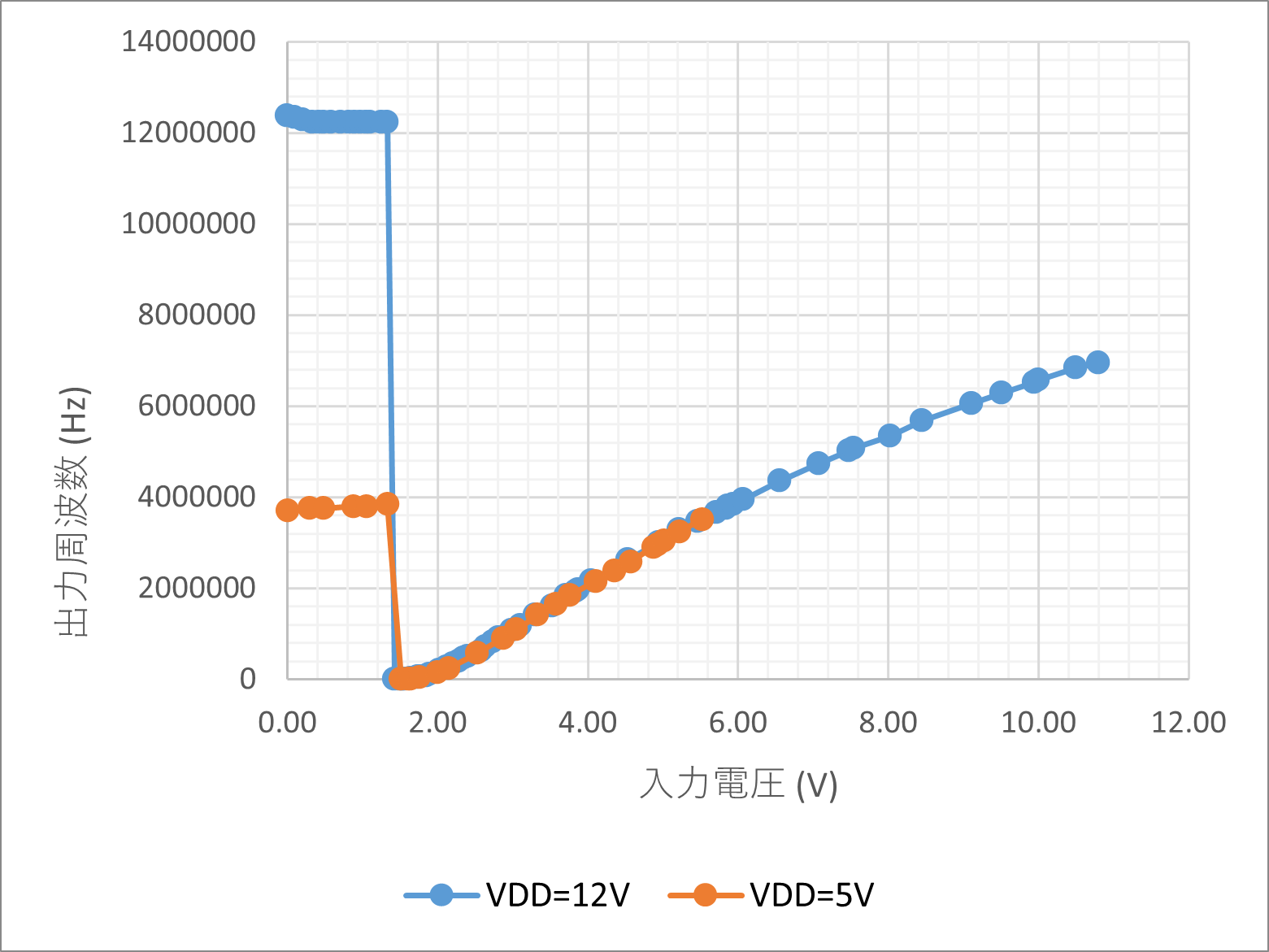

この測定回路を用いて測定したVCOの性能は上図のようになる。図より、VIN > 1.5Vにおいて発振周波数の上限、つまり、VIN > 1.5Vにおける最大の発振周波数は、VDD=5Vで3.516MHz (VIN=5.51V)、VDD=12Vで6.938MHz (VIN=10.8V)であることが確認できる。PLL性能の測定結果について、VDD=5Vの発振周波数が約3MHzで頭打ちになる理由がこれである。また、VDD=12Vにおいて4MHz以上で発振できる。このことは、MC145106のFin (2 pin)の周波数入力にデュアル・バランスド・ミキサ (DBM)を用いて、より高い周波数で発振させることも可能であることを示唆している。

この測定回路を用いて測定したVCOの性能は上図のようになる。図より、VIN > 1.5Vにおいて発振周波数の上限、つまり、VIN > 1.5Vにおける最大の発振周波数は、VDD=5Vで3.516MHz (VIN=5.51V)、VDD=12Vで6.938MHz (VIN=10.8V)であることが確認できる。PLL性能の測定結果について、VDD=5Vの発振周波数が約3MHzで頭打ちになる理由がこれである。また、VDD=12Vにおいて4MHz以上で発振できる。このことは、MC145106のFin (2 pin)の周波数入力にダブル・バランスド・ミキサ (DBM)を用いて、より高い周波数で発振させることも可能であることを示唆している。

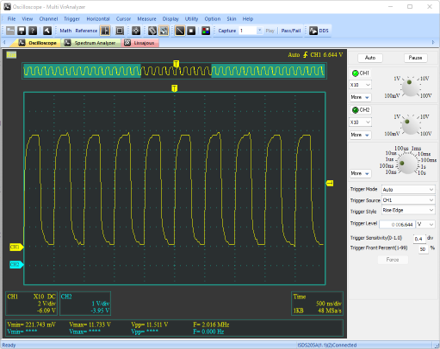

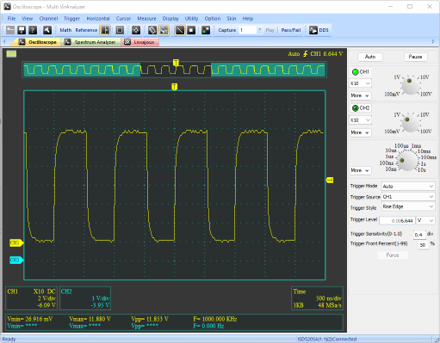

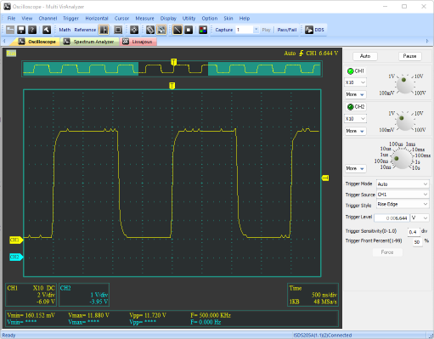

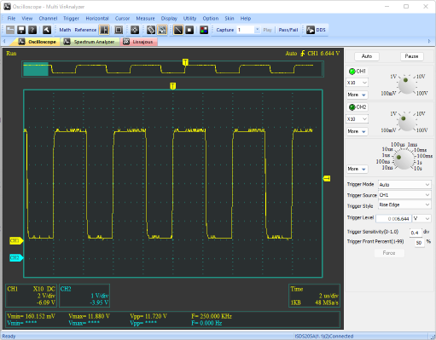

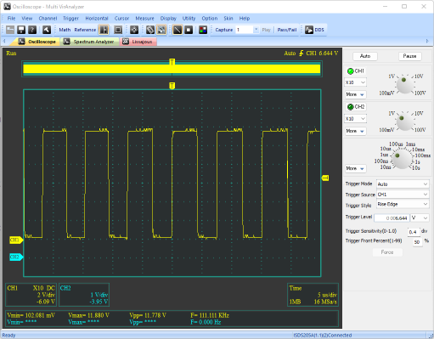

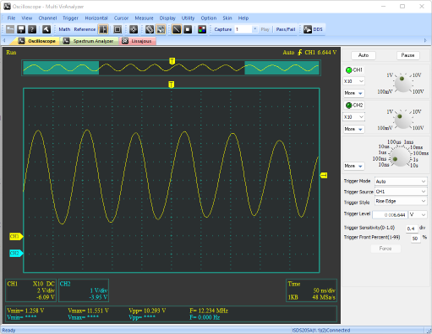

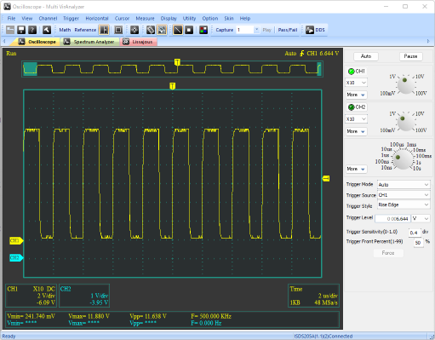

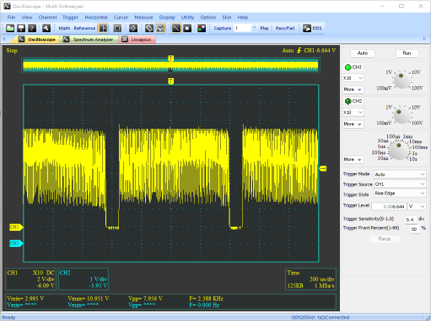

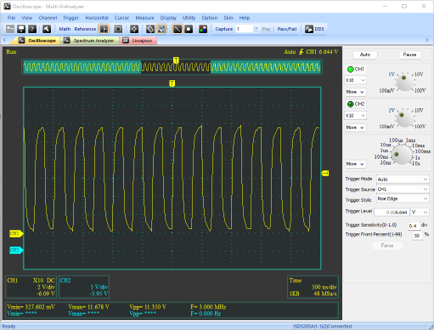

また、このVCOの出力周波数は、VIN=1.5Vを境界に、それ以下ならVINによらずほぼ一定の高周波を出力し、それ以上なら、VINの上昇に比例して発振周波数も高くなっている。このことから、VIN=1.5Vを境に動作モードが変化していると推察できる。この動作モードの変化については、次セクションにてVCOの出力波形を確認し考察する。 ### 発振波形 以下に、VDD=12Vにおける、WaveOutの出力波形を示す。    #### VIN > 1.5Vの場合 波形は矩形波であり、これは、インバータの出力がH/Lに切り替わることで起きた意図した発振であることと推察される。 PLLシンセサイザ―のVCOとして用いている動作は、この領域での動作である。 #### VIN < 1.5V、または、VIN≒1.5Vの場合 VIN < 1.5Vの波形は正弦波 (正確には、正弦波の合成波)であり、これはインバータの出力切り替えでは実現できない動作である。また、VIN≒1.5Vでは、VIN < 1.5VとVIN > 1.5Vにおける動作が合わさったような波形が見られる。これらの波形は、CMOSインバータが、インバータとしてではなく増幅器として動作したことによる、位相発振に起因するものであると考えられる。 # まとめ 本記事では、作成したPLLシンセサイザの回路紹介と性能紹介を行った。 最後に達成事項と今後の課題をまとめる。 ==達成できたこと 1. MC145106とリング発振器を使用し、PLLシンセサイザを制作ことに成功した。 2. 制作したPLLシンセサイザの性能測定を行い、VDD=12Vにおいて最大4MHzの矩形波出力を得ることができた。 3. 制作したVCOの特性を測定し、発振周波数の入力依存性を把握し、PLLシンセサイザ―の性能や拡張性に対する考察を行った。== ++今後の課題

1. デュアル・バランスド・ミキサを使用し、4MHz以上の周波数も設定できるようにすることで、PLLとしての性能の限界を把握すること。

1. ダブル・バランスド・ミキサを使用し、4MHz以上の周波数も設定できるようにすることで、PLLとしての性能の限界を把握すること。

2. VCOを改良し、より低い周波数(可聴域)やより高い周波数(数十MHz以上)で発振ができるようにすること。++