はじめに

注:本記事では、MAX232をメーカー推奨の使用用途とは異なる用途に使用しています。この記事での使用方法に関して製造メーカーへの問い合わせはご遠慮ください。また、本記事の内容を元に回路を検討される場合や追実験をされる場合は十分に注意したうえで行ってください。本記事の内容による部品破損等のいかなる損害に対しても、筆者は責任を負いかねます。前回記事も合わせてご参照ください。

前回投稿したMAX232を正負電源に使用できるかでは、MAX232の出力(T1OUT, T2OUT)に負荷をつないだ時の出力電圧を測定した。この実験によって、複数のMAX232の出力端子をショットキーバリアダイオードを介して並列接続することで、出力電流の増加に対する出力電圧の低下を抑えることができることを確認した。前回記事の実験結果を踏まえ、さらに並列数を増やしたときの傾向を測定したので、本記事でその結果を紹介する。

実験内容

実験用回路

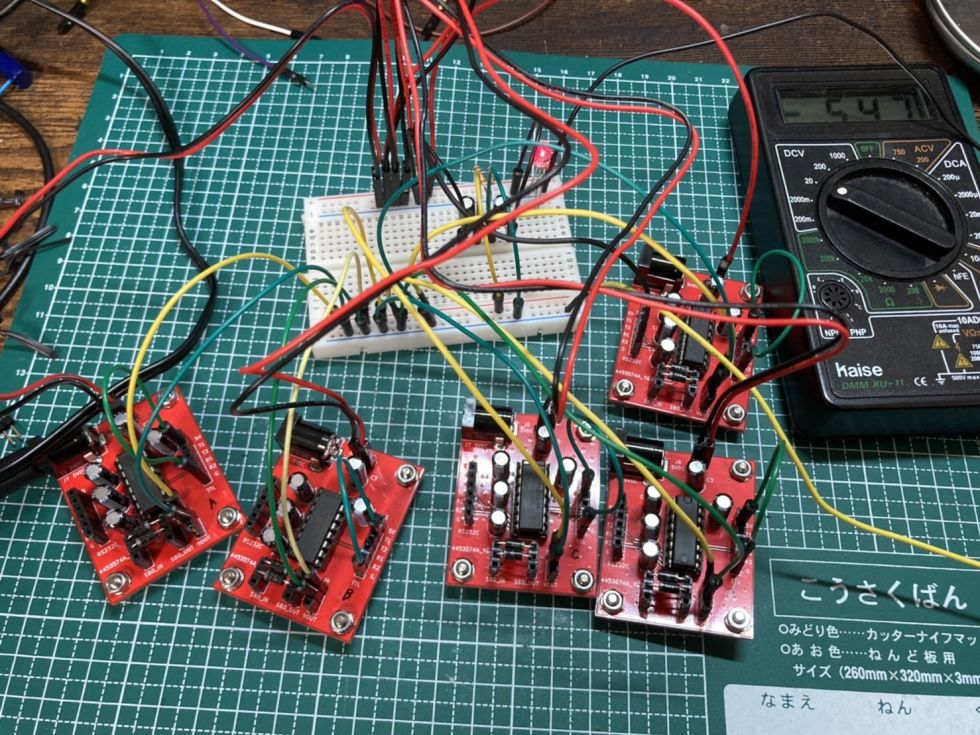

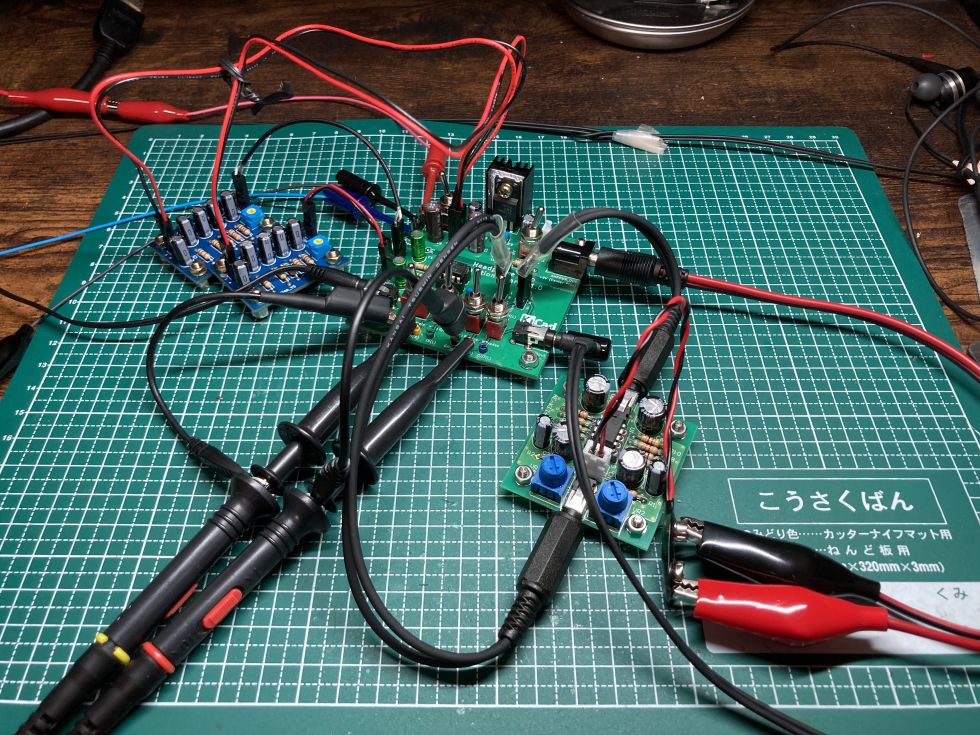

本記事では、下図のようなユニットを複数準備し、各ユニットのV+OUT/V-OUT同士を接続することでMAX232の並列数を増やした。前回記事では出力コンデンサをユニットごとに接続していたが、今回は並列接続した部分(各ユニットのショットキーバリアダイオードの先)に、1個だけ接続している。また、前回は実験回路をすべてブレッドボード上に実装していたが、今回はユニット数が増えるため、各ユニットは次節で説明する実験用ボード上に実装し、ユニット間の接続のみブレッドボードで行った。

実験用ボードの作成

同じ回路を最大5個作成することから、下図のような実験基板を作成した。回路図のJ2, J3はピンソケットで、対応する端子同士でショットキーバリアダイオードを接続することにより、先述の実験用回路を作成することができる。また、RS232C-TTL間インターフェースとしても使用できるように、入出力端子はすべてピンソケットで引き出せるようにした。この回路をPCBに起こしその上に実装することでユニットを作成した。

実験条件

実験に用いる負荷は、前回記事と同じものを用いた。(下表)

| 負荷抵抗 | 負荷電流(概算) |

|---|---|

| 無負荷 | 0 |

| 1MΩ | 9.5uA |

| 100kΩ | 95uA |

| 10kΩ | 0.95mA |

| 4.7kΩ | 2.02mA |

| 10kΩ | 4.32mA |

| 1kΩ | 9.5mA |

| 500Ω(1kΩ並列) | 19mA |

また、ユニットは下表のように5個で、下表のように記号を振ることで区別している。なお、ICの入手状況の関係でユニットA~CはMaxim製を、D~EはTexas Instruments製のものをそれぞれ用いた。

| 記号 | 型番 | メーカー | ユニット単体での無負荷出力電圧 (正側/負側) |

|---|---|---|---|

| A | MAX232CPE | Maxim (現ADI) | 9.35V/-9.72V |

| B | MAX232CPE | Maxim (現ADI) | 9.35V/-9.71V |

| C | MAX232CPE | Maxim (現ADI) | 9.35V/-9.71V |

| D | MAX232N | Texas Instruments | 8.64V/-8.75V |

| E | MAX232N | Texas Instruments | 8.64V/-8.75V |

上記のように、ユニットA,B,CとユニットD,Eの出力電圧が異なるため、下表のように2個のパターンで並列数を増やし、測定結果を比較した。

| 並列数 | パターン1 | パターン2 |

|---|---|---|

| 1 | A | E |

| 2 | A, B | E, D |

| 3 | A, B, C | E, D, C |

| 4 | A, B, C, D | E , D, C, B |

| 5 | A, B, C, D, E | E, D, C, B, A |

実験結果

出力電圧

まず、出力電流に対して出力電圧の関係を示す。グラフの横軸は出力電流を、縦軸は出力電圧を示し、線の色は並列数を表す。

パターン2では、先述のとおり並列数1、2 では出力電圧の低いMAX232Nを用いているので、このときの出力電圧(赤線、橙線)は、パターン2の出力電圧はパターン1と比べて低い。また、同様の理由で、パターン1における並列数3、4、5の出力電圧の上昇幅は、パターン2と比べて低い。さらに、並列数5では接続するユニットに違いがないため、パターン間で出力電圧の変化に差分はない。

パターン1, 2共通の傾向としては、前回記事で予想した通り並列数が増えれば増えるほど、出力電流の上昇時に出力電圧の低下を抑制できることである。この傾向について、次に示すロードレギュレーションで説明する。

ロードレギュレーション

次に、出力電流に対するロードレギュレーションの関係を示す。グラフの横軸は出力電流を、縦軸はロードレギュレーションを示し、線の色は並列数を表す。

ロードレギュレーションΔVOUTは、前回記事と同様、以下の式で計算し、両対数グラフにプロットした。

- ΔVOUT(正電源) = VOUT(無負荷) - VOUT(負荷電流を引いたとき)

- ΔVOUT(負電源) = VOUT(負荷電流を引いたとき) - VOUT(無負荷)

全体の傾向としては、出力電圧のセクションで触れた通り、パターンによらず並列数が増えれば増えるほどロードレギュレーション、つまり出力電圧のドロップが減らせていることがわかる。また、並列数が少ないときは、並列数の増加に対するパターン1での下がり幅が大きくなり、並列数が多いときはパターン2で下がり幅が大きくなる。これは、パターン1では出力電圧の高いMAX232CPEを先に接続した後、出力電圧の低いMAX232Nを接続したのに対し、パターン2ではその逆で接続したためであると考えられる。

また、出力電流=0.0095mAのときに着目すると、パターン1では並列数が増えるとロードレギュレーションが低下しているのに対し、パターン2では逆にロードレギュレーションが上昇していることが読み取れるが、並列数変化に対するロードレギュレーションの変化量0.01Vが、テスターの測定精度0.01Vと等しいため、並列接続数増加に対する回路特性の変化、というよりも、テスターの測定精度に起因した変化であると考えられる。

考察・まとめ

本記事での実験により、前回記事で予測したとおり、MAX232の並列数を増やすことで、電流に対する出力電流のドロップ量、つまりロードレギュレーションを減らすことができることを示した。同様に、接続するICの出力電圧が異なると、並列接続によるロードレギュレーション低減の効果が弱くなることが分かったので、並列接続する場合は、少なくともICのメーカーは統一したほうがよいと思った。

また、並列数を5個まで増やしても、出力電流9.5mAで1.5V程度出力電圧が下がるため、実際に電源として用いる場合は、負荷の消費電流を低く抑えるか、リニアレギュレータなどで出力電圧を安定化させたほうが無難であり、電源としての実用性は低いように感じた。(そもそも、電源用のICではないので当然ではあるが。)

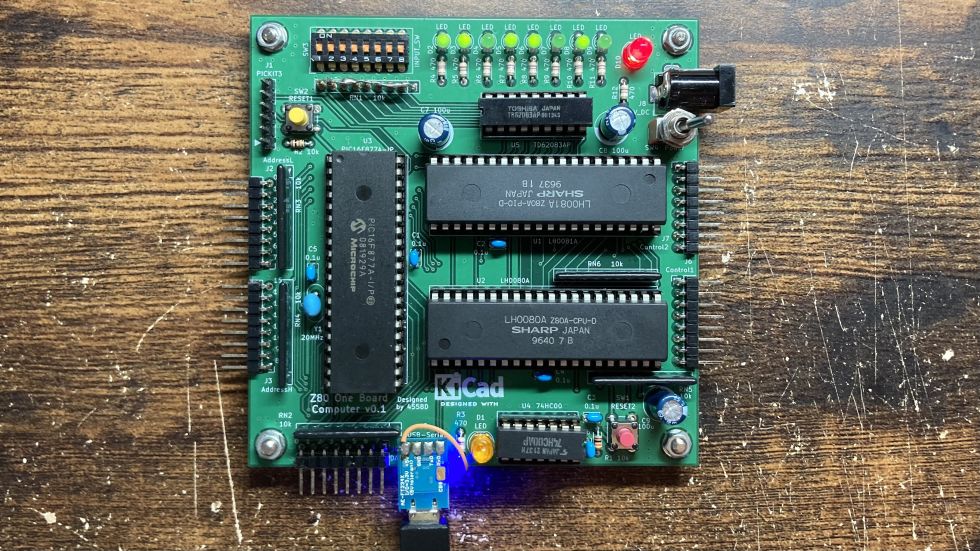

投稿者の人気記事

-

4558D

さんが

2023/01/28

に

編集

をしました。

(メッセージ: 初版)

-

4558D

さんが

2023/01/28

に

編集

をしました。

ログインしてコメントを投稿する