自作CPU Advent Calendar 2022 20日目

TD4の命令を実行できる自作CPU「Kageki」で、パドルの操作でモールス信号を出力するやつを作ってみた。

仕様

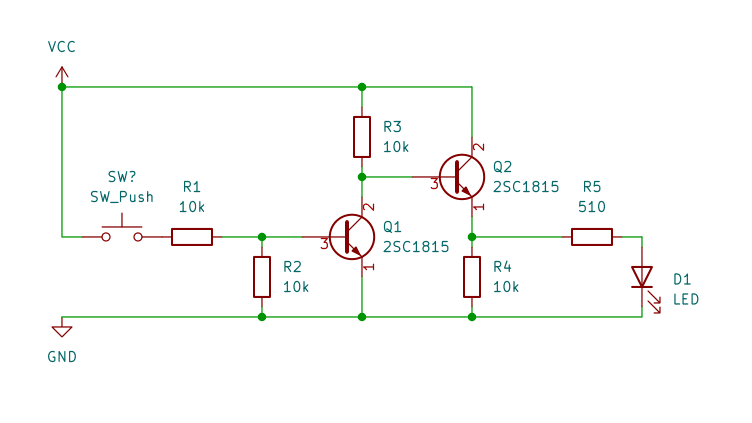

入力ポートのビット2に短点 (左)、ビット3に長点 (右) のスイッチの信号を入力する。

(押されている→HIGH、押されていない→LOW)

出力ポートのビット0にモールス信号が出力される。

(OUT 0001 を OUT 1000 に置き換えればビット3に出力できる)

(ビットの表記は0-origin)

プログラム

位置 機械語 アセンブリ言語

---------------------------------

0 00100000 FIRST: IN A

1 00000100 ADD A, 0100

2 11101010 JNC NOBOTH

3 00010000 SOUND: MOV A, B

4 10110001 WAIT: OUT 0001

5 00000001 ADD A, 0001

6 11100100 JNC WAIT

7 10110000 OUT 0000

8 01011000 ADD B, 1000

9 11110000 JMP FIRST

A 01110100 NOBOTH: MOV B, 0100

B 00000100 LOOP: ADD A, 0100

C 11101110 JNC NOTON

D 11110011 JMP SOUND

E 01011000 NOTON: ADD B, 1000

F 11101011 JNC LOOP動作

0番地で入力を読み込んだ後、以下の動作をする。

- ビット2・ビット3の両方が1の場合

- 1番地の加算ででキャリーが発生し、2番地の条件分岐を通過する

- 現在のBレジスタの値を用いて信号出力処理を行う

- ビット3 (長点) のみ1の場合

- 1番地の加算でAレジスタの上位2ビットは

11となり、2番地からA番地に飛ぶ - A番地でBレジスタを

0100に設定する - B番地の加算でキャリーが発生し、C番地の条件分岐を通過する

- Bレジスタの値

0100を用いて信号出力処理を行う

- 1番地の加算でAレジスタの上位2ビットは

- ビット2 (短点) のみ1の場合

- 1番地の加算でAレジスタの上位2ビットは

10となり、2番地からA番地に飛ぶ - A番地でBレジスタを

0100に設定する - B番地の加算でAレジスタの上位2ビットは

11となり、C番地からE番地に飛ぶ - E番地の加算でBレジスタの値は

1100となり、F番地からB番地に飛ぶ - B番地の加算でキャリーが発生し、C番地の条件分岐を通過する

- Bレジスタの値

1100を用いて信号出力処理を行う

- 1番地の加算でAレジスタの上位2ビットは

- ビット2・ビット3の両方が0の場合

- 1番地の加算でAレジスタの上位2ビットは

01となり、2番地からA番地に飛ぶ - A番地でBレジスタを

0100に設定する - B番地の加算でAレジスタの上位2ビットは

10となり、C番地からE番地に飛ぶ - E番地の加算でBレジスタの値は

1100となり、F番地からB番地に飛ぶ - B番地の加算でAレジスタの上位2ビットは

11となり、C番地からE番地に飛ぶ - E番地の加算でキャリーが発生し、F番地の条件分岐を通過する

- 0番地の入力の読み込みに戻る

- 1番地の加算でAレジスタの上位2ビットは

- 信号出力処理 (共通)

- 3番地でBレジスタの値をAレジスタにコピーする

- 4番地で信号をHIGHにする

- 4~6番地で、Aレジスタに1を足していき、キャリーが発生するまで待つ

- 7番地で信号をLOWにする

- 8番地でBレジスタに

1000を加える。これは同時押し時に短点と長点を交互に出すための切り替えである - 9番地で、0番地の入力の読み込みに戻る

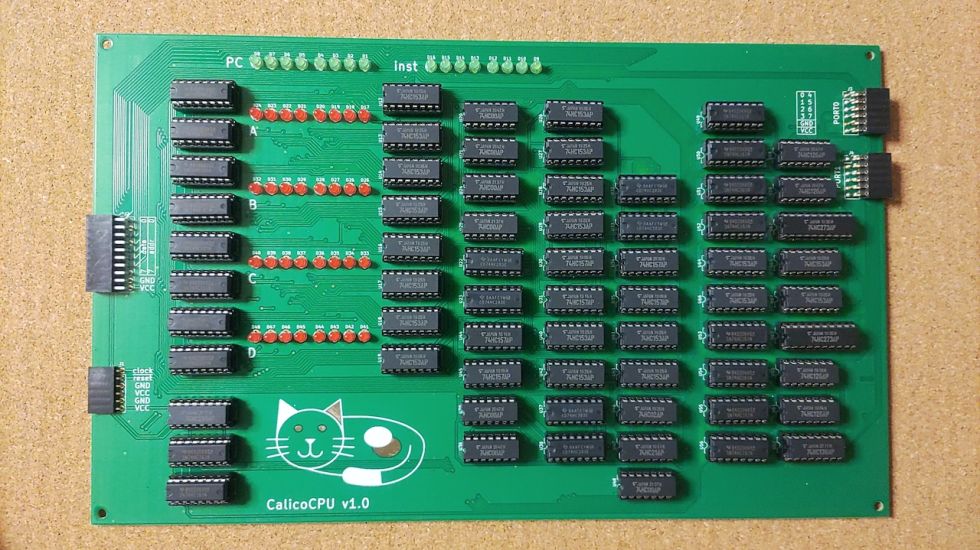

パドル接続基板

KagekiにCW用のパドルを接続するため、3.5mmステレオジャックのLをビット2、Rをビット3、GNDをVCCに接続し、ビット2とビット3をプルダウンする基板を作成した。

実行結果

入力ポートに前述のパドル接続基板を介して CW-ONE を、出力ポートに 2-way Buzzer Board を接続し、200Hz のクロックで実行した。

投稿者の人気記事

-

mikecat

さんが

2022/12/20

に

編集

をしました。

(メッセージ: 初版)

-

mikecat

さんが

2022/12/20

に

編集

をしました。

(メッセージ: アドベントカレンダーのリンク忘れを修正)

ログインしてコメントを投稿する